категории: Препоръчани статии » Практическа електроника

Брой преглеждания: 12919

Коментари към статията: 0

Чип 4046 (K564GG1) за устройства с задържане на резонанс - принципът на работа

При създаване на захранващо електронно устройство с задържане на резонанс в LC веригата е проектирана резонансна верига на контролера за синхронизиране на получените трептения с контролни импулси, идващи от водача.

Задачата на този контролер е да поддържа резонансни трептения в веригата LC, като го вълнува във времето със собствените си трептения. За да постигне това, контролерът трябва да получи сигнал от цикъла от веригата, съдържаща данни за текущата честота и фазата на свободните трептения в него, след което, разчитайки на тези данни, поддържа етап на драйвера в синхронизация с тези честота и фаза, а след това резонанса във веригата ще бъде автоматично записан.

За изграждането на такъв контролер е подходящ чипът CD4046 или неговият вътрешен колега K564GG1. Нека разгледаме устройството на тази микросхема, целта на нейните заключения и схемата на свързване на монтираните компоненти, за да разберем с какво се занимавате, ако е необходимо.

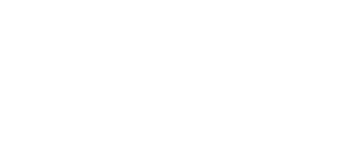

Този чип ви позволява лесно да организирате PLL верига - фазово заключена верига. За изграждането на PLL се използват три необходими блока, които са разположени вътре в микросхемата: осцилатор, управляван от VCO - напрежение, FC - фазов компаратор и LPF - нискочестотен филтър.

Вграден в микросхемата, VCO генерира последователност от правоъгълни импулси с 50% запълване, тоест чиста квадратна вълна, чиято начална честота зависи от параметрите на две RC вериги: R1C1 и R2C2, свързани с нея извън микросхемата, а амплитудата в този случай е близка до захранващото напрежение на микросхемата U +.

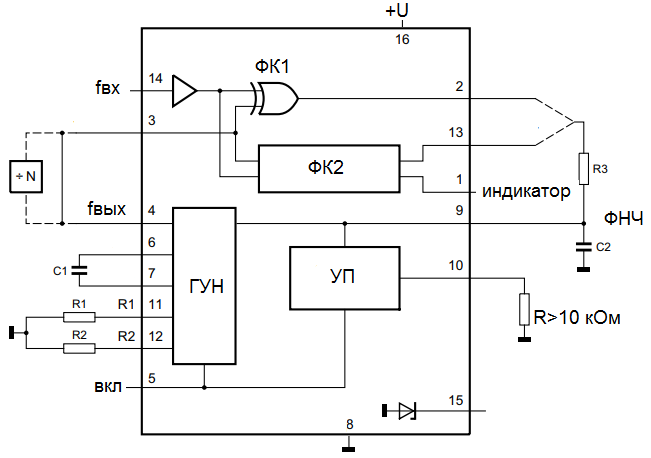

PLL принцип на работа

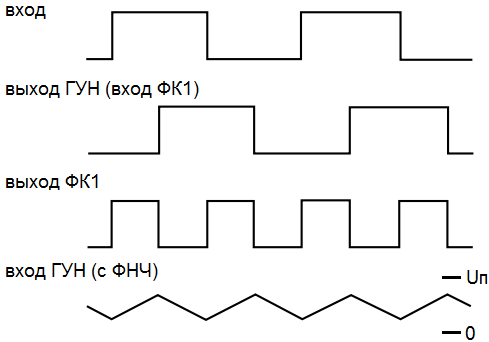

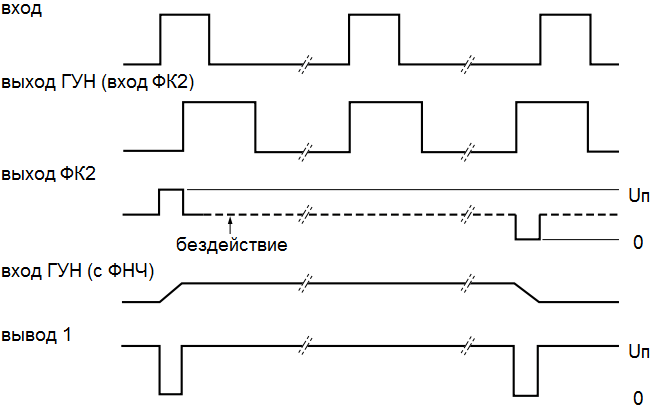

Външният перка на входния сигнал се подава към микросхемата, всъщност към един от входовете на фазовия компаратор FC (FC1 или FC2 - разработчикът избира) вътре в него. Меандър, произведен от VCO, се подава едновременно към втория FC вход. В резултат на това се получава правоъгълен сигнал на изхода на FC, продължителността на импулса в който зависи от разликата между импулсите от VCO и външните импулси във всеки момент от време.

Всъщност продължителността на изходните импулси с FC е пропорционална на фазовата разлика на двата сравнени сигнала. Факт е, че логическият елемент с изключителна ИЛИ често се използва като FC, това означава, че на изхода на FC ще има високо ниво на напрежение, само ако има разлика между сигналите и ако няма разлика, тогава изходът от FC ще бъде нисък ниво на напрежение или неактивно състояние.

От изхода на FC сигналът се подава към нискочестотен филтър, който е проста RC верига, върху кондензатора на който се получава пулсиращо напрежение на несъответствие, като нивото на пулсацията е пропорционално на разликата на двата сигнала (от вътрешния VCO и се подава към микросхемата отвън), всъщност - разликата на фазите ,

Напрежението на несъответствие, получено в кондензатора LPF, веднага се подава обратно към входа на VCO и в зависимост от средната му стойност, честотата на VCO ще бъде автоматично настроена, така че честотата на меандъра на неговия изход fout се приближава до честотата на външния сигнал, идващ от външната страна на микросхемата. При достигане на подобна ситуация средното напрежение в кондензатора на нискочестотния филтър ще бъде най-малкото - това е знак за максимално сближаване на двата сигнала по честота и фаза. Когато сигналът бъде захванат, той ще продължи да се държи от PLL контура.

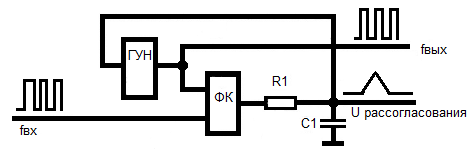

Границите на реорганизацията на VCO

Както вече разбрахте, VCO честотата е в състояние да се настройва в определен диапазон от автоматична настройка. Този диапазон се задава от външните компоненти на чипа. А скоростта на реакция на PLL системата се определя от времевата константа на LFF (стойности C2 и R3).Поради тази причина трябва стриктно да подходите към избора на монтирани компоненти на чипа.

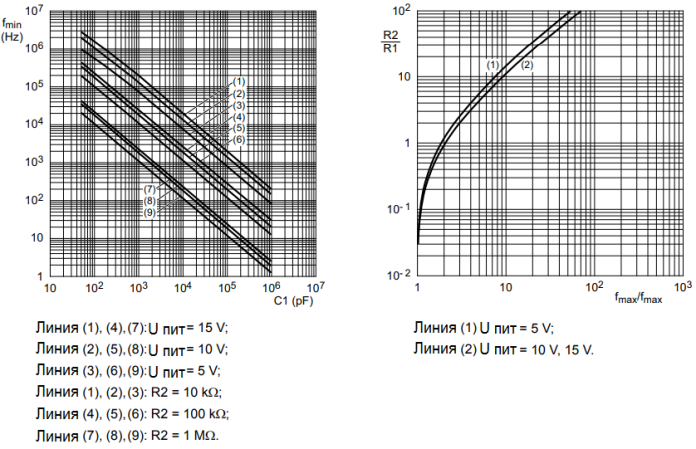

Захранващото напрежение на микросхемата, кондензаторът С1, както и резисторите R1 и R2 определят диапазона на самонастройване на VCO честотата вътре в микросхемата. Резистор R2 отклонява минималната честота fmin на VCO над нулата. А съотношението между стойностите на резисторите R1 и R2 определя съотношението между максималните и минималните честоти - fmax / fmin, регулируем изходен сигнал от VCO.

Чип входове и изходи

Заключение 4 - изходен сигнал на VCO, върху него в работен режим меандър. Този изход може да се използва за подаване на сигнал към други блокове на проектираното устройство.

Пин 5 е отговорен за включването и изключването на VCO. Когато се приложи високо напрежение към този изход, микросхемата ще се изключи. При прилагане на ниско ниво на напрежение (когато свързвате щифт 5 към общия проводник) - микросхемата ще работи в нормален режим.

Заключения 6 и 7. Кондензаторът С1 е свързан с тях - това е кондензатор за настройка на честотата на VCO.

Заключение 8 - общият захранващ проводник на чипа.

Резистор R1 е между клема 11 и общия проводник. Резистор R2 - между клема 12 и общия проводник. Това са честотни резистори за настройка. Резистор R3 на нискочестотния филтър - към щифт 9 и щифт 2 или 13 (разликата между тях ще бъде разгледана по-нататък), кондензаторът С2 на нискочестотния филтър е между щифт 9 и общия проводник.

Пин 10 е изходът на усилвателя на ретранслатора. Напрежението върху него по време на работа на микросхемата е напрежението за несъответствие, подавано към нискочестотния филтър. Заключение 10 е проектирано така, че напрежението при несъответствие може, ако е необходимо, да бъде лесно изолирано без маневриране на кондензатора LPF. Към този извод е позволено да се свърже резистор със съпротивление повече от 10 kOhm.

Заключение 15 - върху него е катодът на вградения ценеров диод със стабилизационно напрежение 5,6 волта (стабилизационното напрежение на този ценеров диод може да бъде различно, в зависимост от производителя на чипа). Този ценеров диод по желание може да се използва в силовата верига на чипа.

Заключение 16 - плюс мощността на чипа.

Входове и изходи на фазови сравнители FC1 и FC2

Меандърът от изхода на VCO се взема от терминал 4 и се подава към клема 3, свързан през усилвател-форматор към входовете на фазовите компаратори FC1 и FC2. По желание сигналът от VCO може по желание да бъде предаден през честотен делител.

Вход 14 е сигнален вход и към него се подава входен сигнал, с който е необходимо да се синхронизира изходният сигнал на изхода на VCO. В зависимост от характера на входния сигнал, разработчикът може да избере кой от фазовите сравнители да използва: FC1 или FC2, и да прикрепи нискочестотен филтърен резистор към избрания компаратор (да закрепи 2 или 13). Фазовият сравнител FC2 има индикаторен щифт 1, напрежение на високо ниво се появява върху него, когато сигналите са максимално синхронизирани.

Особеността на FC1 е, че е прост логически елемент с изключителен ИЛИ, а качеството на работата му зависи от параметрите на нискочестотния филтър на неговия изход. Работата започва с централната честота f0 = (fmax-fmin) / 2, възможно е да се уловят хармониците на централната честота. Има висок имунитет на шум.

Особеността на FC2 е, че той обработва само положителните разлики на импулсите, подадени към него, и следователно работният цикъл на импулсите не е от значение. Работата започва с минималната честота fmin, няма възможност за улавяне на хармониците на централната честота. Има нисък имунитет на шум. В нискочестотния филтър е необходим кондензатор с нисък ток на изтичане. FC2 е по-подходящ за използване в силови вериги с LC резонанс.

Избор на прикачени файлове

Като нискочестотен филтър на нискочестотния филтър се монтират резистор R3 и кондензатор C2. За да работи правилно PLL, постоянната време на RC трябва да бъде десетки пъти по-голяма от приблизителната честота на улавяне на PLL.

Като правило честотата на заснемане е приблизително известна на разработчика, поради което те първоначално се задават от честотния диапазон за автоматично настройване: fmin и fmax. Първата номограма определя, като се вземат предвид захранващото напрежение на микросхемата и необходимия fmin, стойностите на R2 и C1.След това, според втората номограма, на базата на необходимото съотношение fmax / fmin, R1 се избира. По-добре е да осигурите възможност за регулиране на резисторите във веригата.

Вижте също на e.imadeself.com

: