категории: Практическа електроника, Новаци електротехници

Брой преглеждания: 74031

Коментари към статията: 0

Логически чипове. Част 9. JK спусък

История за JK задействане и прости експерименти за изучаване на работата му.

История за JK задействане и прости експерименти за изучаване на работата му.

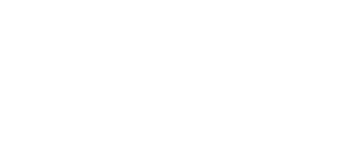

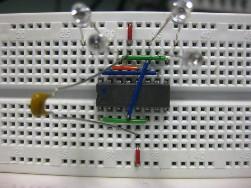

В предишните части на статията бяха описани задействания като RS и D. Тази история ще бъде непълна, ако не споменете Jk спусък, Както и D спусък Той има разширена логика на въвеждане. В серията 155 това е чип K155TV1, произведен в пакета DIP-14. Нейната фиксация, или както се казва сега, pinout (от английския PIN - pin) е показана на фигура 1a. Чужди аналози SN7472N, SN7472J.

Ако в определена схема не се използва някакво заключение, тогава е напълно приемливо просто да не се показва, както е показано на фигура 1б.

Описание и цел на заключенията

Спусъкът на K155TV1 има директни и обратни изходи. На фигурата това са съответно заключения 8 и 6. Целта им е същата като при предишните разглеждани спусъци от тип D и RS. Обратният изход започва в малък кръг.

При входовете R и S спусъкът работи точно като обикновен RS спусък, Работното ниво на тези входове е ниско, което се обозначава с кръгове в основата на клемите. Подобно на D-тригера, тези входове са приоритетни: появата и задържането на ниско ниво на един от тях инхибира работата на останалите входове и кратък отрицателен импулс ще прехвърли спусъка в съответното състояние до следващия импулс на вход C.

Входът C е синхронизиран. Когато спусъкът работи в режим на броене, той играе ролята на информационния - именно върху него пристигат броещи импулси. В режима на получаване и съхраняване на информация, той служи като часовник, предназначението му е подобно на подобен вход на D-тригер, но логиката на работа е малко по-различна и се определя от състоянието на JK входовете.

Фигура 1. Разбивка на чипа K155TV1.

J и K са контролни входове на спусъка. Те се комбинират съгласно схема 3I, която е обозначена със символа & - логически I. на графичния символ. Доста често тези входове просто се свързват в схемите, оказва се, че има един J и един K вход. Някои серии микросхеми също имат JK задействания, те се наричат също TB1, но за разлика от серията 155 имат един J и K вход. Логиката на работа на тези входове е абсолютно същата като тази на K155TV1, но не е необходимо да събирате 3 логически сигнала от високо ниво заедно. Пример за такива микросхеми може да служи например K176TV1, K561TV1, K1564TV1.

Научаване на логиката на JK спусъка

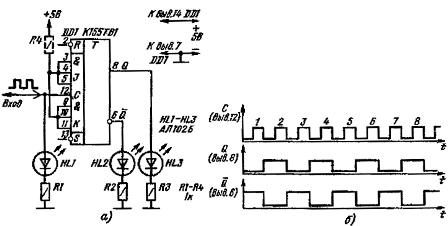

За да се запознаете по-подробно с работата на JK спусъка, просто трябва да го включите, както в предишната статия, на дъската и ръчно да приложите входните сигнали. Всъщност трябва да признаете, че можете да запомните ръководство за самоподготовка за свирене на китара или акордеон на бутон, но без да вземете инструмента, няма да се научите да свирите. Също и в случая на микросхеми: докато не проведете най-простите експерименти, ще бъде трудно да разберете смисъла на работата.

Като входни сигнали, точно както при изучаване на тригер D, ще използваме теленен джъмпер, свързан към общ проводник.

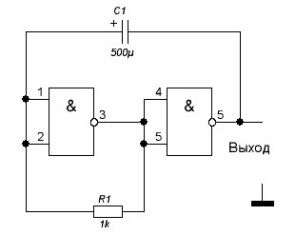

Схемата за тестване на JK тригера K155TV1 е показана на фигура 2.

Фигура 2. Тест JK тригер K155TV1.

Захранващото напрежение се подава както обикновено към 14-ия и 7-ия изводи на микросхемата, което е показано на диаграмата под формата на проводници със стрелки.

За визуално наблюдение на състоянието на спусъка към неговите изходи са свързани директни и обратни, LED индикатори. Същият индикатор е свързан към вход С. Светодиодният блясък показва наличието на ниво логическа единица (2.4 ... 5V) на този изход. На входа С ще се покаже нивото на изходния сигнал на генератора на импулси, свързан към входа С. Разбира се, състоянието на входовете и изходите при такава ниска честота е напълно възможно да се наблюдава с обикновен волтметър, но това не е много удобно.

JK задействане на RS - входове

Въпреки че веригата се оказа много проста, преди да я включите, както обикновено, трябва да я проверите за грешки, късо съединение и прекъсвания: дори само включването на захранването в обратна посока може да направи микросхемата неизползваема. Това правило трябва да се помни и да се прилага във всички подобни случаи, дори ако това е само електрическа верига без полупроводникови устройства.

Затова го включете. Когато за първи път включите, един от светодиодите на изхода трябва да свети, което е неизвестно. Това се дължи на преходни процеси, когато са включени. Сега ще приложим ниско логическо ниво, използвайки гореспоменатите жични джъмпери, редуващо се към входовете R и S. В този случай светодиодите на изхода трябва последователно да се превключват, което показва състоянието на спусъка. Този режим на работа се нарича асинхронен - не изисква допълнителни строб сигнали (активиране, часовник).

Не е необходимо едновременно да се прилага ниско ниво директно към входовете R и S: това състояние се счита за забранено за спусъка. Въпреки че това няма да доведе до необратими последици под формата на изход на микросхемата, състоянието на изходите в този случай ще бъде неизвестно, което не съответства на логиката на спусъка. Ако всичко е наред, тогава можете да отидете на експерименти за изучаване на работата на тригер на JK входовете.

Какво се случва, ако към входовете JK се приложи ниска жица с джъмперна жица? Изобщо нищо: спусъкът ще запази предишното състояние, което ще се вижда по сиянието на индикаторите. За да могат тези входове да повлияят на състоянието на спусъка, е необходимо да се приложат импулси към входа C от генератора, чиято верига е показана на фигура 3. За да се сглоби, е необходим допълнителен чип K155LA3. Скоростта и продължителността на импулса трябва да са такива, че да е възможно визуално наблюдение на състоянията на задействане.

Фигура 3. Генератор на часовник.

JK задействане в режим на броене

Ако входовете JK са свързани, както е показано на фигура 2а, тогава спусъкът ще работи в режим на броене: състоянието на спусъка ще се промени с всеки входен импулс. Резисторът R4 е показан на диаграмата с пунктирана линия - не можете да го поставите, защото несвързаните входове все още са в състояние на логическа единица. Основната цел на този резистор е да предпазва от смущения чрез входовете на JK.

Времевата диаграма на JK тригера е показана на фигура 2b и е много подобна на подобна схема за D - тригера. Основната разлика е, че състоянието на спусъка не се променя поради положителна разлика в нивото на вход C, а отрицателно - когато нивото на входния импулс се променя от високо ниво на ниско.

Лесно е да се види, че честотата на импулсите на изхода на спусъка е точно два пъти по-ниска от честотата на входните импулси. Затова тригерите в режим на броене често се използват като разделители на честотата по две. Два включени в серията тригери ще разделят честотата на четири, а три задействания вече ще бъдат разделени на осем и така нататък според силата на 2.

Ако е необходим честотен делител с коефициент на нечетно разделение, тогава се използват няколко задействания с обратна връзка, но това ще бъде разгледано в следващата част на статията относно броячите и импулсните форми.

От горното можем да заключим: ако входовете на JK са едновременно в състояние на логическа единица (високо ниво), спусъкът работи в режим на броене. Това означава, че за всяка отрицателна разлика в нивото на вход C състоянието на спусъка се променя на обратното.

Задействане на JK входове

Какво се случва, ако едновременно на входовете на JK присъства логическо нулево ниво? За да проверите това, достатъчно е да свържете поне един JK вход (припомнете, че K155TV1 има 3 J и 3 K входове, комбинирани съгласно 3I схема) към общ проводник. Но можете да се свържете с общия проводник и всички входове на JK, това е безпринципно. Според LED индикаторите виждаме, че импулсите на часовника идват, а състоянието на спусъка не се променя.В състояние, когато логическата нула на входовете J и K, JK - тригерът е в режим на съхранение на информация.

Остава да разгледаме два случая. Първият случай е, когато входът J е голям, а входът K е нисък. В тази ситуация спусъка на вход C е настроен на едно състояние - индикаторът HL3, свързан с директния изход на спусъка, светва. HL2, разбира се, се изплаща.

Ако състоянието на входовете на JK не се промени в бъдеще, тогава всеки импулс на входа C също ще има тенденция да задава тригера на едно състояние, въпреки че вече е в него. В този случай те казват, че на входа С предишното състояние на спусъка в този случай просто се потвърждава.

Вторият случай е, когато входът J е нула, а входът K е един. В това състояние, при входовете на JK, първия импулс на вход C, спусъкът ще бъде настроен на нула (нулиране) - индикаторът HL3 ще се изключи и HL2 ще се включи. Ако състоянието на JK входовете не се промени, тогава входът C също потвърждава състоянието, както е описано по-горе, само този път нула.

И така, за по-лесно запомняне, да обобщим: две единици на входовете на JK е режим на броене. Разбира се, че условие 3I е изпълнено за входовете JK: един на трите входа J и един на трите входа K.

Две нули на JK входовете - режим на съхранение на информация: импулсите на вход C на състоянието на спусъка не могат да бъдат променени. За получаване на такова състояние е достатъчно поне един вход J И поне един вход K да има логическо нулево ниво.

В случай, че и трите J - входа са високи, спусъка се задава на едно състояние. В същото време поне един от 3-те входа на K трябва да има ниско ниво.

За нулиране на спусъка трябва да има нула на поне един от входовете J и един трябва да се задържи на трите входа K.

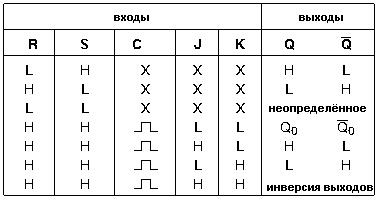

Всичко, което беше написано по-горе, може да бъде намерено в таблицата за истинност на спусъка K155TV1, която е показана на Фигура 4.

Фигура 4. Таблицата за истинност за чипа K155TV1.

Задействанията от различни видове се използват също като елементи на броещи устройства или просто броячи, както и като импулсни оформящи. Това ще бъде разгледано в следващата част на статията за логическите схеми.

Продължение на статията: Логически чипове. Част 10. Как да се отървем от отскока от контактите

Електронна книга -Ръководство за начинаещи за AVR микроконтролери

Вижте също на e.imadeself.com

: