ประเภท: วงจรไมโครคอนโทรลเลอร์

จำนวนการดู: 21445

ความเห็นเกี่ยวกับบทความ: 0

FPGA คืออะไรภาษาง่าย ๆ สำหรับผู้เริ่มต้น

อุปกรณ์อิเล็กทรอนิกส์ดิจิทัลเกี่ยวข้องกับอะไร? ก่อนอื่นมีองค์ประกอบทางตรรกะ AND, OR, NOT เพิ่มเติมลงทะเบียนเปลี่ยนเครื่องถอดรหัสมัลติเพล็กเซอร์ ฯลฯ เข้ามาในหน่วยความจำ อย่างไรก็ตามเมื่อความซับซ้อนของอุปกรณ์อิเล็กทรอนิกส์และแนวโน้มเพิ่มขึ้นเป็นขนาดเล็กการสร้างอุปกรณ์ที่ใช้วงจรรวม (ไอซี) จากส่วนประกอบข้างต้นกลายเป็นเรื่องยากยิ่งขึ้นไอซีที่กำหนดเองของโครงสร้างและวงจรที่ต้องการนั้นพิสูจน์ได้ว่าคุ้มค่าเฉพาะเมื่ออุปกรณ์

ทางออกของสถานการณ์นี้คือการพัฒนาวงจรตรรกะแบบรวมที่ตั้งโปรแกรมได้ (ย่อมาจาก FPGA, ตัวย่อต่างประเทศเป็นอุปกรณ์ตรรกะที่โปรแกรมได้, PLD) มันคืออะไรและมันใช้ที่ไหนเราจะบอกในบทความนี้

ความแตกต่างจากไมโครคอนโทรลเลอร์

ด้วยคำว่า "โปรแกรมได้" ผู้เริ่มต้นส่วนใหญ่จะเชื่อมโยง กับไมโครคอนโทรลเลอร์. แม้ว่าที่จริงแล้วพวกเขาจะได้รับการตั้งโปรแกรมไว้ FPGA ก็เป็นอุปกรณ์ที่แตกต่างกัน

สำหรับนักพัฒนาในไมโครคอนโทรลเลอร์ชุดโซลูชั่นและเครื่องมือแบบคงที่นั้นมีอยู่ซึ่งมีอยู่ในชิปตัวใดตัวหนึ่งโดยเฉพาะมันจะไม่ทำงานในลักษณะที่จะหนีจากสถาปัตยกรรม คุณจะได้รับชุดคำสั่งที่คุณใช้ดำเนินการเกี่ยวกับสภาพแวดล้อมโดยการอ่านข้อมูลจากอินพุตดิจิตอลและอนาล็อกและการส่งสัญญาณไปยังแอคทูเอเตอร์โดยใช้เอาต์พุต

นอกจากนี้คุณสามารถทำการคำนวณบันทึกข้อมูลในรีจิสเตอร์หรือ ROM รวมทั้งทำงานกับข้อมูลที่กระพริบลงในหน่วยความจำของไมโครคอนโทรลเลอร์ โดยพื้นฐานแล้วนี่คือจุดประสงค์และคุณสมบัติของการทำงานกับไมโครคอนโทรลเลอร์

วงจรรวมแบบลอจิกแบบโปรแกรมได้ (FPGAs) จะแตกต่างกันเมื่อคุณตั้งโปรแกรมอุปกรณ์ด้วยตัวคุณเองคุณจะสร้างสถาปัตยกรรมจากองค์ประกอบตรรกะพื้นฐาน ดังนั้นคุณจะได้รับความเร็วสูงและความยืดหยุ่นของชิป สิ่งนี้ทำให้เป็นไปได้โดยไม่เปลี่ยนชิปหนึ่งตัวเพื่อสร้างโครงการจำนวนหนึ่ง

โดยทั่วไปอุปกรณ์ FPGA ภายในสามารถแบ่งออกเป็นสามกลุ่มหลัก:

1. อาร์เรย์ขององค์ประกอบตรรกะ (macrocells บล็อกตรรกะ)

2. บล็อกอินพุต / เอาต์พุต (IO)

3. สายสื่อสารระหว่างกันกับอุปกรณ์ที่ควบคุมการเชื่อมต่อเหล่านี้

อย่างไรก็ตามการจัดโครงสร้างดังกล่าวเป็นแบบทั่วไปมากเราจะพิจารณาปัญหานี้ในรายละเอียดเพิ่มเติมด้านล่าง

โดยการเขียนโปรแกรมคุณจะเชื่อมต่อองค์ประกอบต่าง ๆ ในลักษณะเดียวกันกับที่คุณใช้ประกอบอุปกรณ์จากแต่ละองค์ประกอบและเชื่อมต่ออินพุตและเอาท์พุตเข้ากับตัวนำ

หมายเหตุ:

ความแตกต่างที่สำคัญระหว่าง FPGA และไมโครคอนโทรลเลอร์คือในไมโครคอนโทรลเลอร์คุณไม่สามารถเปลี่ยนการเชื่อมต่อภายในระหว่างองค์ประกอบที่ง่ายที่สุดและการเขียนโปรแกรมและการทำงานกับพวกมันนั้นขึ้นอยู่กับการลงทะเบียนการเชื่อมต่อใน FPGA

ตัวเลือกของไมโครคอนโทรลเลอร์ขึ้นอยู่กับเกณฑ์หลายอย่างเช่น:

-

ความเร็วและความเร็วนาฬิกา

-

ปริมาณของ ROM และ RAM

-

จำนวนอินพุตและเอาต์พุต

คุณสมบัติการทำงานอื่น ๆ และอุปกรณ์ต่อพ่วงเช่นการสนับสนุนสายการสื่อสารและโปรโตคอล (I2C, หนึ่งสาย, สัญญาณ PWM, ฯลฯ )

เมื่อเลือก FPGA เกณฑ์หลักคือจำนวนบล็อกที่ตั้งโปรแกรมได้ - มันควรจะเพียงพอที่จะใช้งาน

จำนวนบล็อกอาจแตกต่างกันอย่างมากและค่าใช้จ่ายก็เปลี่ยนแปลงตามทั้งนี้ขึ้นอยู่กับ FPGA ที่ระบุ

ไมโครคอนโทรลเลอร์ดำเนินการตามลำดับการดำเนินการทั้งหมดที่กำหนดไว้ในโปรแกรมในขณะที่บล็อก FPGA จะทำงานแบบขนานและเป็นอิสระจากกันดังนั้นการเปรียบเทียบอุปกรณ์เหล่านี้ด้วยความถี่สัญญาณนาฬิกาจึงไม่สามารถใช้งานได้ หลักการทำงานของพวกเขาแตกต่างกันมากเกินไป

ประเภท

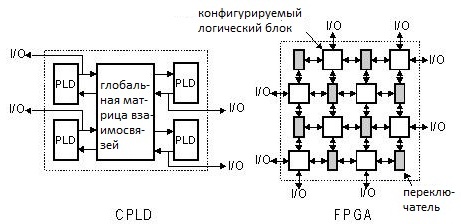

ปัจจุบันเกี่ยวข้องกับ FPGA สองประเภทหลัก:

1. CPLD (อุปกรณ์ที่ตั้งโปรแกรมได้ซับซ้อน - วงจรรวมที่ตั้งโปรแกรมได้จริง ๆ แล้วนี่คือ FPGA ในแง่ของความคลาสสิค) มันมักจะมีหน่วยความจำที่ไม่ลบเลือนภายในซึ่งโหลดเฟิร์มแวร์

โครงสร้างภายในสร้างขึ้นจากเมทริกซ์ของมาโครเซลหรือบล็อกเชิงตรรกะและจำนวนองค์ประกอบในนั้นอยู่ในช่วงร้อยและหลายพันชิ้น เนื่องจากความเรียบง่ายแบบสัมพัทธ์จึงมีราคาถูกกว่าตรรกะชนิดโปรแกรมชนิดถัดไป ทั้งหมดนี้นำไปสู่ความจริงที่ว่า CPLD ใช้เป็นหลักในวงจรที่ต้องการความเร็วสูงและเอาต์พุตจำนวนมากในขณะที่ทำงานง่าย

2. FPGA (Array Gate-Programmable Array - Array Gate ที่ตั้งโปรแกรมได้โดยผู้ใช้ แต่มักเรียกว่า FPGA) - อุปกรณ์ที่ได้รับการพัฒนาและมีความซับซ้อนมากขึ้นเมื่อเทียบกับ CPLD ถูกสร้างขึ้นบนบล็อกโลจิคัลพร้อมการสลับแบบยืดหยุ่นและมีองค์ประกอบจำนวนมากขึ้น (ชิ้นส่วนนับหมื่นหรือหลายแสนชิ้น)

โดยปกติเฟิร์มแวร์จะถูกเก็บไว้ในหน่วยความจำที่ไม่ลบเลือนภายนอก นอกเหนือจากองค์ประกอบตรรกะที่ง่ายที่สุดแล้ว FPGAs สามารถมีบล็อกสำเร็จรูปสำหรับการดำเนินการใด ๆ เช่นบล็อกการประมวลผลสัญญาณ DSP ทั้งหมดนี้ช่วยให้คุณสามารถใช้โปรเซสเซอร์อุปกรณ์ประมวลผลสัญญาณและอุปกรณ์ที่ซับซ้อนอื่น ๆ

น่าแปลกใจฉัน:

แม้ว่าในความเป็นจริงแล้วการมีอยู่ของหน่วยความจำแบบไม่ลบเลือนไม่ได้ทำให้ตรรกะของโปรแกรม CPLD นี่เป็นบางส่วนที่ทำให้เข้าใจผิด ความแตกต่างที่สำคัญระหว่าง CPLD และ FPGA คือโครงสร้างภายใน

อุปกรณ์ CPLD ภายในแสดงรายละเอียดเพิ่มเติมในรูปด้านล่าง

และรูปแบบโดยประมาณของ macrocell มีลักษณะดังนี้:

macrocell ประกอบด้วยมัลติเพล็กเซอร์ที่สามารถตั้งโปรแกรมทริกเกอร์ (หนึ่งหรือมากกว่า) และสร้างกลุ่มสัญญาณเอาท์พุต FB ในหลายรุ่น

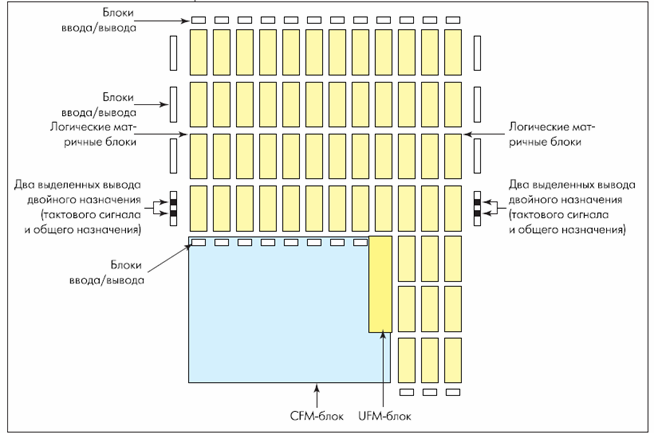

ต่อไปนี้เป็นอีกตัวอย่างหนึ่ง - บล็อกไดอะแกรมของชิป CPLD จากตระกูลชิป Altera MAX II

และแผนโครงสร้างของชิปของตระกูลเดียวกัน

ยางระดับกลางจะถูกกำหนดให้กับ macrocells โดยใช้โหนดเช่นผู้จัดจำหน่ายเป็นภาษาอังกฤษ มันดูเหมือนลอจิกตัวจัดสรรซึ่งแสดงในแผนภาพด้านล่างมันยังแสดงเมทริกซ์ของการสลับ (Global Routing Pool) และที่ macrocells เอาท์พุท (macrocells) มีสองข้อเสนอแนะ

เอาท์พุทภายนอกของ microcircuit เชื่อมต่อกับเอาท์พุทของ macrocells ผ่านบล็อกอื่น (เมทริกซ์) - ORP (สระว่ายน้ำเส้นทางการส่งออก) โปรดทราบว่าผ่าน INPUT ตรรกะเชื่อมต่อกับ GRP ดังแสดงในภาพด้านล่าง

หมายเหตุ:

CPLD บางส่วนมีสิ่งที่เรียกว่า อินพุตโดยตรง (อินพุตโดยตรง) - พวกเขาเชื่อมต่อกับอินพุตของเซลล์โดยตรงซึ่งจะช่วยลดความล่าช้า

โครงสร้าง FPGA มีรูปแบบ:

-

L - บล็อกกำหนดตรรกะ

-

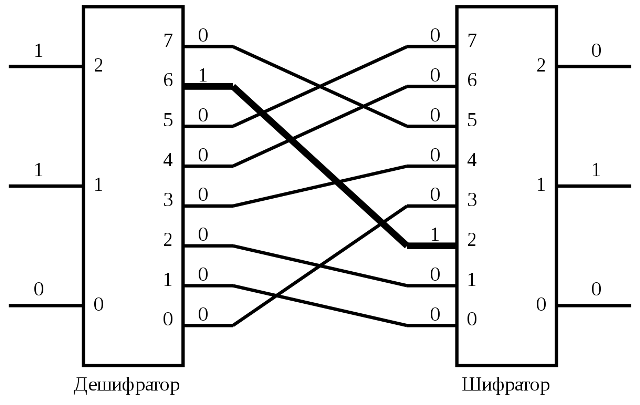

S (บล็อกการแทนที่) - บล็อกการแทนที่มันจะได้รับจำนวนบิตต่อการย้ายที่แน่นอนตามขั้นตอนวิธีที่แน่นอนและส่งออกจำนวนบิตที่แตกต่างกันที่เอาต์พุต กล่าวอีกนัยหนึ่งคือตัวถอดรหัสตัวเข้ารหัสและสวิตช์

-

C (บล็อกการเชื่อมต่อ) - บล็อกการเชื่อมต่อ

แผนภาพ S-block:

การเขียนโปรแกรม

HDL (ภาษาคำอธิบายฮาร์ดแวร์) - นี่คือภาษาที่มีโปรแกรม FPGA ยอดนิยมและหลากหลายคือ Verilog HDL และ VHDL มีภาษาอื่น ๆ เช่นภาษาเฉพาะสำหรับผู้ผลิตเช่น AHDL สำหรับผลิตภัณฑ์ ALTERA

การเขียนโปรแกรมกราฟิกมีให้สำหรับนักพัฒนาที่ทำงานกับ FPGA นั่นคือคุณสามารถวาดวงจรตรรกะหรือรวมรหัสกับกราฟิก หลังถูกเรียกว่าวิธีการพัฒนาแบบแยกส่วนเมื่อมีการกำหนดโมดูลเฉพาะและโมดูลด้านบนซึ่งทุกอย่างถูกรวมเข้าด้วยกันจะถูกโปรแกรมแบบกราฟิก

ตัวอย่างของผู้ผลิตและซีรีส์ยอดนิยม

ในช่วงเวลาของการเขียนที่มีชื่อเสียงที่สุดคือผลิตภัณฑ์ของผู้ผลิตสองราย

-

Altera (ก่อตั้งขึ้นในปี 1983);

-

Xilinx (ก่อตั้งขึ้นในปี 1984)

Altera มีตรรกะที่ตั้งโปรแกรมได้หลายชุด:

-

MAX, MAX II, MAX IIZ;

-

7000S;

-

3000A;

-

สูงสุด V;

-

พายุไซโคลน;

-

Arria;

-

Stratix

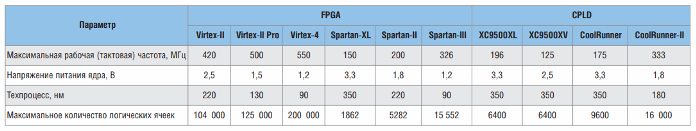

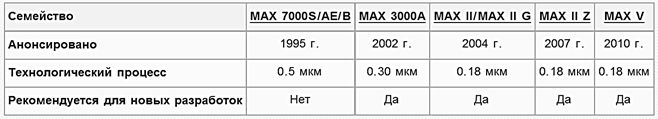

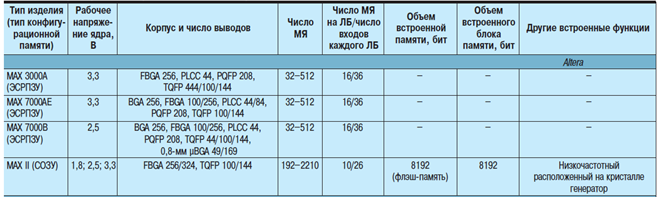

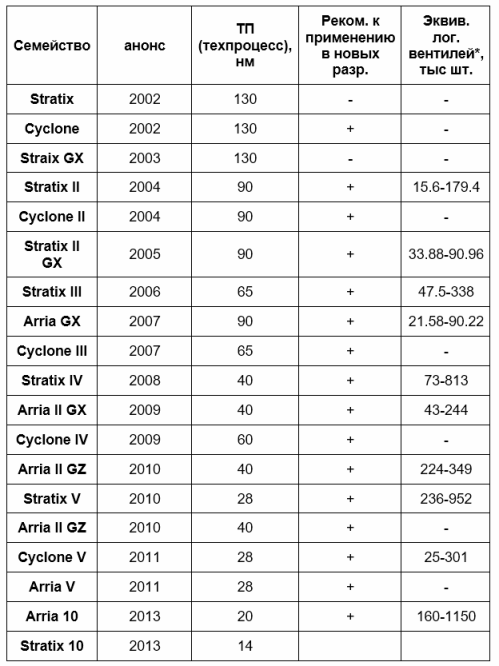

ลองพิจารณาแต่ละคนอย่างละเอียด ในตารางด้านล่างคุณจะเห็นข้อมูลทั่วไปเกี่ยวกับชิปของตระกูล

Altera 3 CPLD CPLD:

-

MAX เป็น CPLD สำหรับใช้ในอุปกรณ์พกพาจุดเด่นคือการใช้พลังงานต่ำและการกระจายความร้อน ขึ้นอยู่กับความซับซ้อนและการปล่อยปีการปรับเปลี่ยนต่อไปนี้จะแตกต่าง:

-

7000S ล้าสมัยไปแล้วและเผยแพร่ในปี 1995

-

3000A - เปิดตัวในปี 2002 ผลิตโดยใช้เทคโนโลยี 300nm ประกอบด้วยมาโครเซลล์จำนวนเล็กน้อย (32-512)

-

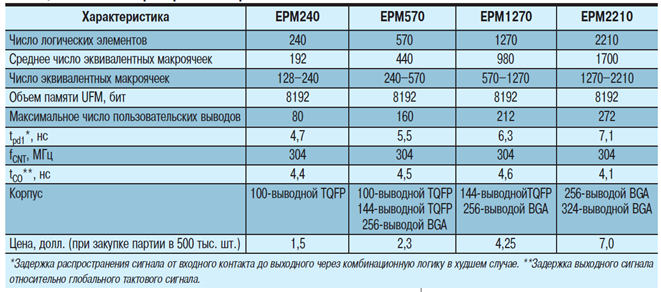

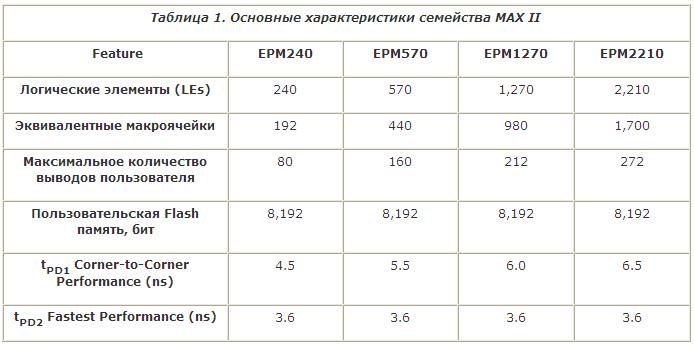

MAX II เปิดตัวในปี 2004 ผลิตขึ้นโดยใช้เทคโนโลยี 100 นาโนเมตรประกอบด้วยหน่วยจำนวนมากขึ้น (240-2210) ทำงานที่ความถี่สูงถึง 304 MHz ผลิตภัณฑ์นี้ผลิตในกรณีของประเภท TQFP 0.5 มิลเลอร์ที่มีขา 100 ขึ้นไป

-

MAX IIZ - 2007 คุณสมบัติหลักคือลดการใช้พลังงาน - นี่คือจุดบวกอย่างไรก็ตามความถี่จะลดลงเป็น 152 MHz Microcircuits เหล่านี้ใช้พลังงานจาก 1.8 V

-

MAX V - 2010 ปี มันถูกผลิตขึ้นตามเทคโนโลยี 180nm มันสามารถมีได้ตั้งแต่ 40 ถึง 2210 บล็อกและทำงานที่ความถี่สูงถึง 152MHz หรือที่ 304MHz ขึ้นอยู่กับจำนวนบล็อก

FPGA:

-

Cyclone เป็นชิพประเภท FPGA ราคาประหยัด มีห้าชั่วอายุคนที่ถูกทำเครื่องหมายด้วยตัวเลขกรีก (จาก I ถึง V ตามลำดับ) รุ่นแรกเปิดตัวในปี 2545 ผลิตโดยใช้เทคโนโลยี 180nm และรุ่นที่ห้าเปิดตัวในปี 2554 และผลิตโดยใช้เทคโนโลยี 28nm เป็นที่น่าสังเกตว่าทุกรุ่นยังคงมีความเกี่ยวข้อง

-

Arria - อ้างถึง FPGA ระดับกลาง

-

Stratix - FPGA ที่ทรงพลัง

ด้านล่างนี้เป็นตารางเดือยลอจิกที่ตั้งโปรแกรมได้ของ Altera FPGA

และตารางเต็มได้ที่ลิงค์:https://e.imadeself.com/th/tablitsa.docx

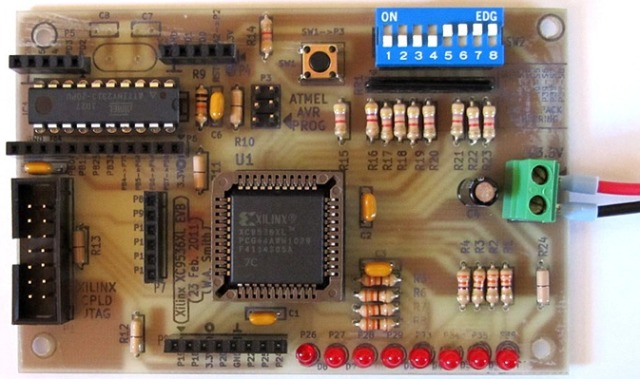

ผู้ผลิต Xilinx CPLD นำเสนอในซีรีส์:

-

XC9500XL จาก macrocells 36-288 พวกมันทำงานที่ความถี่สูงถึง 178 MHz และรุ่นที่ 288 macrocells ที่ 208 MHz มันทำในกรณีเล็ก ๆ ที่มี 44 พิน (สายรอ) ที่ระยะ 0.8 มม. จากกัน - กรณีเช่นนี้ถือว่าง่ายต่อการบัดกรี นอกจากนี้ยังมีขา 64 และ 100 เพิ่มทีละ 0.5 มม. รวมถึงรุ่นในกล่องหุ้ม PLCC-type

-

CoolRunner-II Series เป็น CPLD ที่ประหยัดพลังงานและมีประสิทธิผล คุณสมบัตินี้ใช้พลังงานจากแรงดันไฟฟ้า 1.8V อินพุตและเอาต์พุตออกแบบมาเพื่อทำงานในช่วง 1.5-3.3V พวกเขาประกอบด้วย macrocells 32-512 และผลิตโดยใช้เทคโนโลยี 180nm ขึ้นอยู่กับจำนวนของเซลล์พวกมันทำงานในช่วงความถี่ที่ 179-323 MHz และยิ่งเซลล์มีขนาดเล็กก็จะยิ่งทำงานได้มากขึ้นในกรณีนี้ พวกมันถูกพบในหลาย ๆ กรณีรวมถึงการบัดกรีได้ง่ายเช่นเดียวกับในวงจรไมโครซีรีส์ที่พิจารณาข้างต้น

บริษัท Xilinx ไม่ผ่านและ FPGA:

-

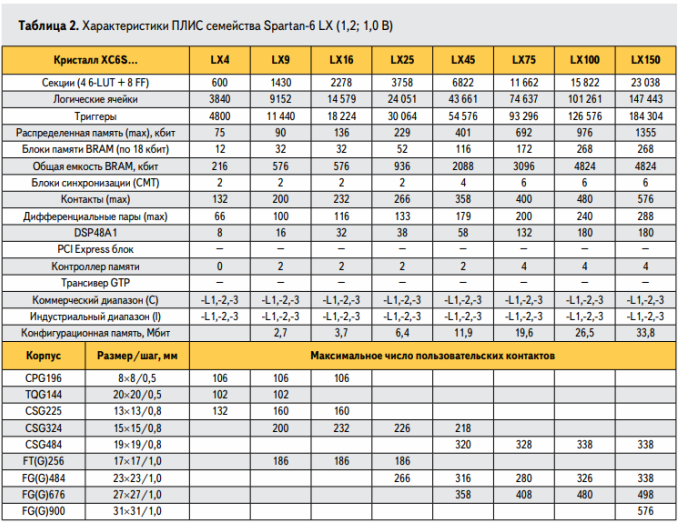

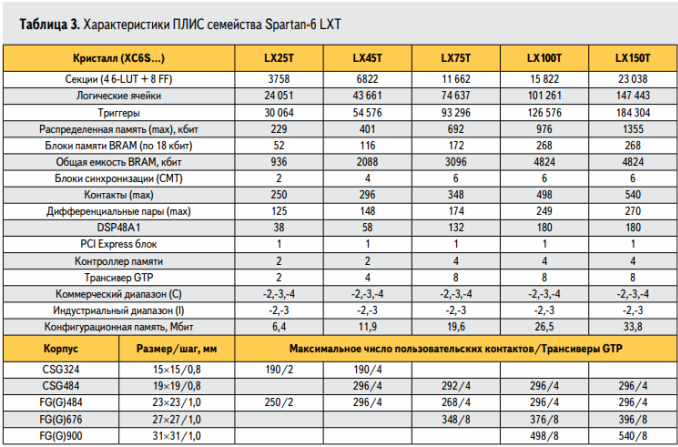

Spartan-6 - ประกอบด้วยบล็อคลอจิก 6 อินพุตจำนวนของพวกเขาอยู่ในช่วง 3840-147443 ชิ้น น่าสนใจว่าพวกเขาอาจมีตัวควบคุมสำหรับการแลกเปลี่ยนข้อมูลเช่น DDR2, DDR3, PCI-EXPRESS, Ethernet 1Gbit, SerialATA ฯลฯ ...

-

ซีรีย์ Vitrex-7 นั้นซับซ้อนวงจรไมโครสามารถมีลอจิกบล็อกได้มากถึง 2,000,000 บล็อกและ 1,200 หน้าสัมผัส

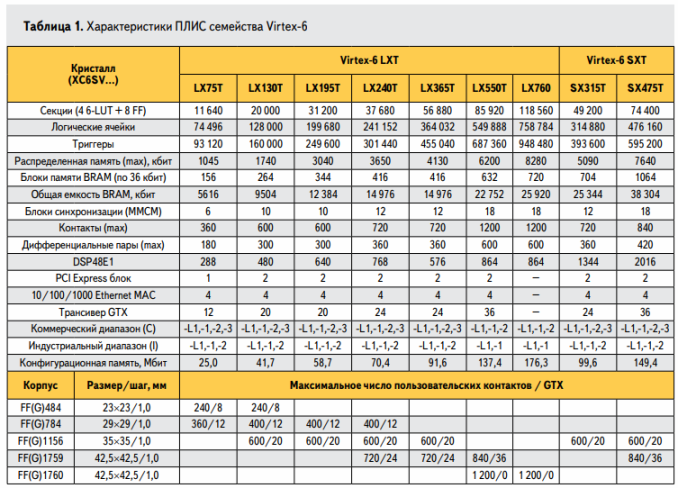

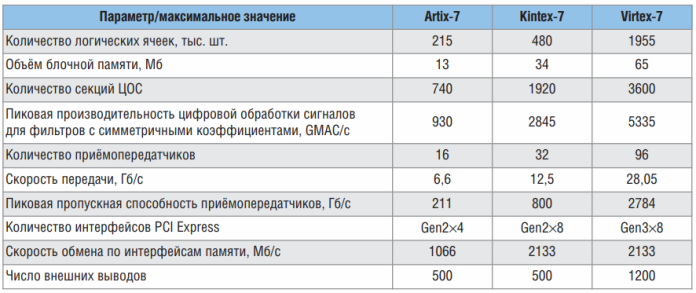

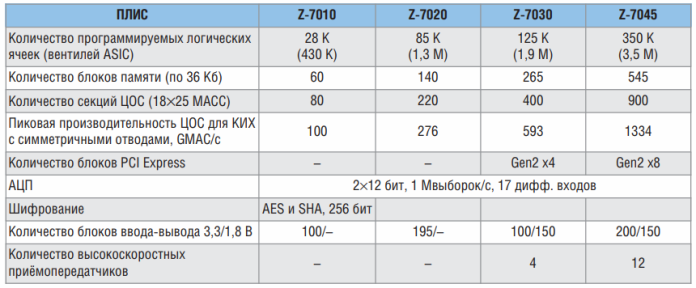

ด้านล่างนี้คุณสามารถค้นหาตารางสรุปด้วยข้อกำหนด CPLD และ FPGA จากซีรีส์ Xilinx 6 และ 7 รวมถึง Zynq-7000

ข้อสรุป

FPGA และ PCVM ผลิตโดย บริษัท อื่นเช่น Lattice Semiconductor (ในปี 2545 เริ่มผลิต FPGAs), Actel และผู้อ่านที่รู้จักกันดีในเว็บไซต์ของเรา ไมโครคอนโทรลเลอร์ ATMEL และอื่น ๆ อีกมากมาย บนตรรกะที่ตั้งโปรแกรมได้มีความเป็นไปได้ที่จะนำอุปกรณ์จำนวนหนึ่งมาใช้ในการคำนวณแบบขนานโดยไม่ขึ้นต่อกันในอุปกรณ์เดียวอย่างไรก็ตามสำหรับโครงการบ้านการซื้อของพวกเขามักไม่ยุติธรรมทางการเงิน แต่ค่อนข้างสมเหตุสมผลในระดับการผลิต

ป.ล.ดูวิดีโอในนั้นคุณจะเห็นตัวอย่างของการใช้งานเกมคอนโซล Nintendo บน FPGA:

ดูได้ที่ e.imadeself.com

: