ประเภท: บทความเด่น » อิเล็กทรอนิคส์ในทางปฏิบัติ

จำนวนการดู: 12919

ความเห็นเกี่ยวกับบทความ: 0

ชิป 4046 (K564GG1) สำหรับอุปกรณ์ที่มีการเก็บเสียงด้วยคลื่น - หลักการทำงาน

เมื่อสร้างอุปกรณ์อิเล็กทรอนิกส์กำลังที่มีการกำทอนสัญญาณในวงจร LC วงจรตัวควบคุมพ้องจะถูกออกแบบมาเพื่อซิงโครไนซ์ที่ได้รับพร้อมพัลส์ควบคุมที่มาจากไดรเวอร์

หน้าที่ของคอนโทรลเลอร์นี้คือการทำให้ออสซิลเลชันแบบสั่นพ้องในวงจร LC ด้วยความตื่นเต้นในเวลาที่มีออสซิลเลชันของตัวเอง เพื่อให้บรรลุสิ่งนี้ผู้ควบคุมจะต้องได้รับสัญญาณจากลูปจากวงจรที่มีข้อมูลเกี่ยวกับความถี่ปัจจุบันและเฟสของออสซิลเลชันอิสระในนั้นหลังจากนั้นใช้ข้อมูลเหล่านี้ในการดูแลขั้นตอนของไดรเวอร์ ในวงจรจะถูกบันทึกโดยอัตโนมัติ

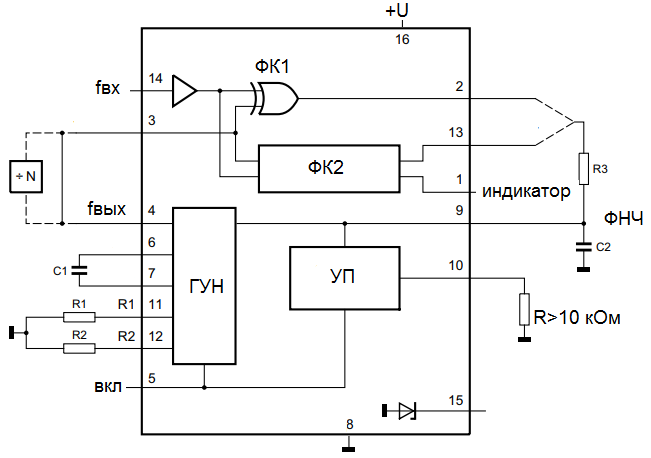

ในการสร้างตัวควบคุมดังกล่าวชิพ CD4046 หรือ K564GG1 ในประเทศนั้นจะเหมาะสม ลองดูที่อุปกรณ์ของ microcircuit นี้จุดประสงค์ของข้อสรุปและไดอะแกรมการเชื่อมต่อของส่วนประกอบที่ประกอบเข้าด้วยกันเพื่อทำความเข้าใจกับสิ่งที่คุณกำลังทำอยู่หากจำเป็น

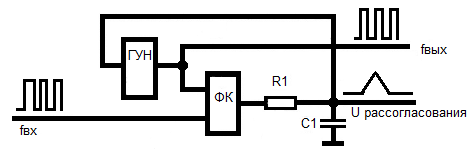

ชิปนี้ช่วยให้คุณสามารถจัดระเบียบ PLL - ลูปล็อกเฟสได้อย่างง่ายดาย ในการสร้าง PLL มีการใช้บล็อกที่จำเป็นสามชุดซึ่งอยู่ภายในไมโครวงจร: VCO - เครื่องควบคุมแรงดันไฟฟ้าที่ควบคุมแรงดันไฟฟ้า, FC - ตัวเปรียบเทียบเฟสและตัวกรอง LPF ต่ำ

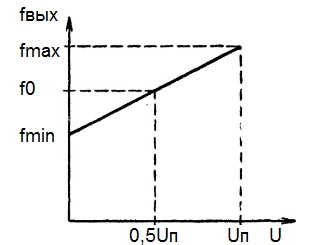

Built-in microcircuit, VCO สร้างลำดับของพัลส์รูปสี่เหลี่ยมผืนผ้าที่มีการครอบคลุม 50% นั่นคือคดเคี้ยวบริสุทธิ์ที่มีความถี่เริ่มต้นขึ้นอยู่กับพารามิเตอร์ของวงจร RC สองตัว: R1C1 และ R2C2 เชื่อมต่อกับมันนอก microcircuit และแอมพลิจูดในกรณีนี้ U +

หลักการทำงานของ PLL

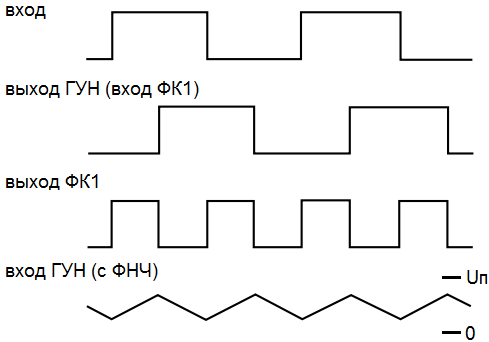

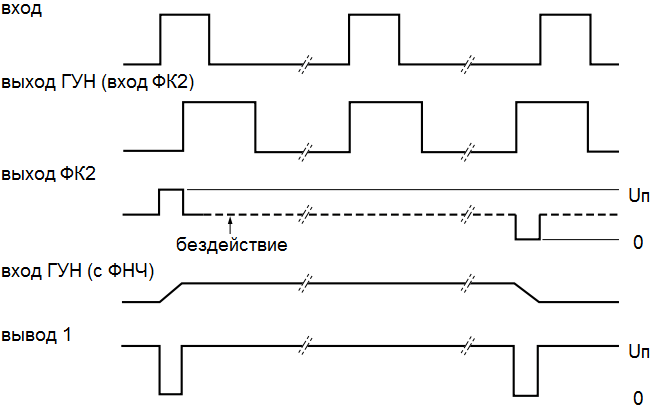

ครีบสัญญาณอินพุตภายนอกถูกจ่ายให้กับไมโครเซอร์กิตในความเป็นจริงแล้วหนึ่งในอินพุตของเฟสตัวเปรียบเทียบเฟส FC (FC1 หรือ FC2 - ผู้พัฒนาเลือก) ที่อยู่ภายใน คดเคี้ยวที่ผลิตโดย VCO นั้นจะถูกป้อนไปยังอินพุต FC ที่สองพร้อมกัน เป็นผลให้ได้รับสัญญาณรูปสี่เหลี่ยมผืนผ้าที่เอาท์พุท FC ระยะเวลาการเต้นของชีพจรซึ่งขึ้นอยู่กับความแตกต่างระหว่างพัลส์จาก VCO และพัลส์ภายนอกในแต่ละช่วงเวลา

ในความเป็นจริงระยะเวลาของพัลส์เอาต์พุตด้วย FC นั้นเป็นสัดส่วนกับความแตกต่างของเฟสของสัญญาณเปรียบเทียบทั้งสอง ความจริงก็คือว่าองค์ประกอบพิเศษ -OR หรือตรรกะมักจะใช้เป็น FC ซึ่งหมายความว่าที่เอาท์พุทเอฟซีจะมีระดับแรงดันสูงเฉพาะในกรณีที่มีความแตกต่างระหว่างสัญญาณและถ้าไม่มีความแตกต่างจากเอฟซีจะต่ำ ระดับแรงดันไฟฟ้าหรือสถานะไม่ใช้งาน

จากเอาต์พุตของ FC สัญญาณจะถูกส่งไปยังตัวกรอง low-pass ซึ่งเป็นวงจร RC แบบง่ายบนตัวเก็บประจุที่แรงดันไม่ตรงกันเร้าใจจะได้รับระดับระลอกเป็นสัดส่วนกับความแตกต่างของสัญญาณทั้งสอง (จาก VCO ภายในและจ่ายให้กับ microcircuit จากภายนอก) .

แรงดันไฟฟ้าที่ไม่ตรงกันที่ได้รับที่ตัวเก็บประจุ LPF จะถูกป้อนกลับไปยังอินพุต VCO ทันทีและขึ้นอยู่กับค่าเฉลี่ยความถี่ VCO จะถูกปรับโดยอัตโนมัติเพื่อให้ความถี่ของคดเคี้ยวที่ขาออกของมันเข้าใกล้ความถี่ของสัญญาณภายนอกที่มาจาก เมื่อถึงสถานการณ์นี้แรงดันเฉลี่ยทั่วตัวเก็บประจุของฟิลเตอร์ low-pass จะเล็กที่สุด - นี่เป็นสัญญาณของการเริ่มต้นของการบรรจบกันสูงสุดของสัญญาณทั้งสองในความถี่และเฟส เมื่อจับสัญญาณแล้วสัญญาณ PLL จะยังคงอยู่ต่อไป

ข้อ จำกัด ของการปรับโครงสร้างองค์กรของ VCO

ตามที่คุณเข้าใจแล้วความถี่ VCO สามารถปรับได้ภายในช่วงการปรับอัตโนมัติ ช่วงนี้ถูกกำหนดโดยส่วนประกอบภายนอกของชิป และความเร็วปฏิกิริยาของระบบ PLL จะถูกกำหนดโดยค่าคงที่เวลาของ LFF (ค่า C2 และ R3)ด้วยเหตุนี้คุณจึงควรเลือกส่วนประกอบที่ยึดของชิปอย่างเคร่งครัด

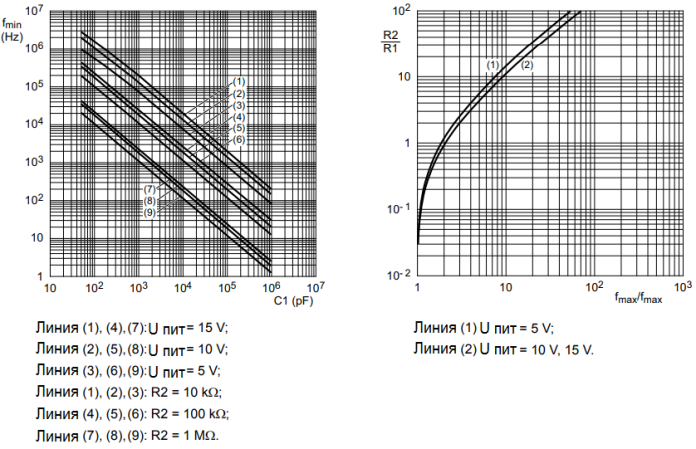

แรงดันไฟฟ้าของ microcircuit ตัวเก็บประจุ C1 รวมทั้งตัวต้านทาน R1 และ R2 เป็นตัวกำหนดช่วงการปรับความถี่ VCO ภายในตัวเองภายใน microcircuit ตัวต้านทาน R2 จะให้อคติความถี่ต่ำสุดของ VCO ที่สูงกว่าศูนย์ และอัตราส่วนระหว่างค่าของตัวต้านทาน R1 และ R2 จะกำหนดอัตราส่วนระหว่างความถี่สูงสุดและความถี่ต่ำสุด - fmax / fmin สัญญาณที่สามารถปรับได้จาก VCO

อินพุตและเอาต์พุตของชิป

สรุป 4 - สัญญาณเอาท์พุตของ VCO ที่อยู่ในโหมดการทำงานคดเคี้ยว เอาต์พุตนี้สามารถใช้เพื่อส่งสัญญาณไปยังบล็อกอื่นของอุปกรณ์ที่ออกแบบ

Pin 5 มีหน้าที่เปิดและปิด VCO เมื่อแรงดันไฟฟ้าระดับสูงถูกนำไปใช้กับเอาท์พุทนี้ microcircuit จะปิด เมื่อใช้ระดับแรงดันไฟฟ้าต่ำ (เมื่อเชื่อมต่อขา 5 กับสายสามัญ) - ไมโครเซอร์กิตจะทำงานในโหมดปกติ

สรุป 6 และ 7 ตัวเก็บประจุ C1 เชื่อมต่อกับพวกเขา - นี่คือตัวเก็บประจุการตั้งค่าความถี่ของ VCO

บทสรุป 8 - สายไฟทั่วไปของชิป

ตัวต้านทาน R1 อยู่ระหว่างขั้ว 11 และสายสามัญ Resistor R2 - ระหว่างเทอร์มินอล 12 และสายสามัญ เหล่านี้คือตัวต้านทานการตั้งค่าความถี่ Resistor R3 ของ low-pass filter - เพื่อ pin 9 และ pin 2 หรือ 13 (ความแตกต่างระหว่างพวกเขาจะกล่าวถึงในภายหลัง) ตัวเก็บประจุ C2 ของ low-pass filter อยู่ระหว่าง pin 9 และ wire ทั่วไป

Pin 10 คือเอาท์พุทของแอมป์ repeater แรงดันไฟฟ้าในระหว่างการทำงานของ microcircuit คือแรงดันไฟฟ้าที่ไม่ตรงกันที่จ่ายให้กับตัวกรอง low-pass สรุป 10 ได้รับการออกแบบเพื่อให้สามารถแยกแรงดันไฟฟ้าที่ไม่ตรงกันออกได้อย่างง่ายดายหากไม่จำเป็นต้องแยกตัวเก็บประจุ LPF ออก ในการสรุปนี้อนุญาตให้เชื่อมต่อตัวต้านทานกับความต้านทานมากกว่า 10 kOhm

สรุป 15 - บนมันเป็นแคโทดของไดโอดซีเนอร์ในตัวที่มีแรงดันเสถียรภาพที่ 5.6 โวลต์ (แรงดันเสถียรภาพของซีเนอร์ไดโอดนี้อาจแตกต่างกันไปขึ้นอยู่กับผู้ผลิตชิป) ซีเนอร์ไดโอดตัวเลือกนี้สามารถใช้ในวงจรพลังงานของชิป

บทสรุป 16 - บวกพลังของชิป

อินพุตและเอาต์พุตของตัวเปรียบเทียบเฟส FC1 และ FC2

คดเคี้ยวจากเอาท์พุทของ VCO นั้นนำมาจากเทอร์มินอล 4 และป้อนไปยังเทอร์มินัล 3 ซึ่งเชื่อมต่อผ่านเครื่องขยายสัญญาณเสียงไปยังอินพุตของตัวเปรียบเทียบเฟส FC1 และ FC2 หากต้องการสัญญาณจาก VCO สามารถเลือกที่จะส่งผ่านตัวแบ่งความถี่

อินพุต 14 เป็นสัญญาณอินพุตและสัญญาณอินพุตถูกป้อนเข้าซึ่งจำเป็นต้องซิงโครไนซ์สัญญาณเอาต์พุตที่เอาต์พุตของ VCO ผู้พัฒนาสามารถเลือกตัวเปรียบเทียบเฟสที่จะใช้: FC1 หรือ FC2 และแนบตัวต้านทานตัวกรองความถี่ต่ำผ่านไปยังตัวเปรียบเทียบที่เลือก (ไปที่ขา 2 หรือ 13) ขึ้นอยู่กับลักษณะของสัญญาณอินพุต เครื่องเปรียบเทียบเฟส FC2 มีพินตัวบ่งชี้ 1 แรงดันไฟฟ้าระดับสูงจะปรากฏขึ้นเมื่อสัญญาณซิงโครไนซ์สูงสุด

ความผิดปกติของ FC1 คือมันเป็นองค์ประกอบตรรกะแบบเอกสิทธิ์เฉพาะบุคคล OR แบบง่ายและคุณภาพของการทำงานขึ้นอยู่กับพารามิเตอร์ของตัวกรอง low-pass ที่เอาต์พุต งานเริ่มต้นด้วยความถี่กลาง f0 = (fmax-fmin) / 2 เป็นไปได้ที่จะจับเสียงประสานของความถี่กลาง มันมีภูมิคุ้มกันเสียงรบกวนสูง

ความผิดปกติของ FC2 คือการประมวลผลเฉพาะความแตกต่างในเชิงบวกของพัลส์ที่ส่งมอบให้และดังนั้นรอบการทำงานของพัลส์จึงไม่สำคัญ งานเริ่มต้นด้วยความถี่ต่ำสุดต่ำสุดไม่มีความเป็นไปได้ในการรวบรวมเสียงประสานของความถี่กลาง มีเสียงรบกวนต่ำ ในฟิลเตอร์กรองความถี่ต่ำจำเป็นต้องมีตัวเก็บประจุที่มีกระแสไฟรั่วต่ำ FC2 เหมาะสำหรับการใช้งานในวงจรไฟฟ้าที่มี LC ด้วยการสั่นพ้อง

การเลือกสิ่งที่แนบมา

ในฐานะที่เป็น low-pass filter ของ low-pass filter ตัวต้านทาน R3 และตัวเก็บประจุ C2 จะถูกติดตั้ง เพื่อให้ PLL ทำงานอย่างถูกต้องค่าคงที่เวลา RC ต้องมากกว่าสิบเท่าของความถี่ในการจับ PLL โดยประมาณ

ตามกฎแล้วความถี่ในการจับภาพนั้นเป็นที่ทราบกันโดยทั่วไปของนักพัฒนาดังนั้นพวกเขาจะถูกกำหนดโดยช่วงความถี่การปรับอัตโนมัติ: fmin และ fmax โนโมแกรมแรกกำหนดโดยคำนึงถึงแรงดันไฟฟ้าของไมโครเซอร์กิตและค่า fmin ที่ต้องการคือค่า R2 และ C1จากนั้นตามโนโมแกรมที่สองตามอัตราส่วน fmax / fmin ที่ต้องการ R1 จะถูกเลือก มันจะดีกว่าเพื่อให้ความสามารถในการปรับตัวต้านทานในวงจร

ดูได้ที่ e.imadeself.com

: