Kategorijas: Mikrokontrolleru shēmas

Skatījumu skaits: 21445

Komentāri par rakstu: 0

Kas ir FPGA - vienkārša valoda iesācējiem

Ar ko ir saistīta digitālā elektronika? Pirmkārt, ar loģiskiem elementiem UN, VAI, NAV. Turklāt atmiņā nonāk maiņu reģistri, dekodētāji, multipleksori utt. Tomēr, pieaugot elektronisko ierīču sarežģītībai un tendencei uz miniaturizāciju, no iepriekšminētajiem komponentiem kļuva sarežģītāk izveidot no integrētajām shēmām (IC) balstītas ierīces, nepieciešamās topoloģijas un shēmas pielāgotas IC izrādījās vērtīgas tikai tad, kad ierīci replicēja lielā skaitā, citos gadījumos tā bija nepamatoti dārga.

Izeja no šīs situācijas bija programmējamu integrētu loģisko shēmu attīstība (saīsināti kā FPGA, ārzemju saīsinājumi kā programmējamas loģiskās ierīces, PLD). Kas tas ir un kur tas tiek izmantots, mēs pastāstīsim šajā rakstā.

Atšķirības no mikrokontrolleriem

Ar vārdu "programmējams" asociējas vairums iesācēju ar mikrokontrolleriem. Neskatoties uz to, ka tie ir arī ieprogrammēti, FPGA ir pilnīgi atšķirīga ierīce.

Izstrādātājiem mikrokontrolleros ir pieejams fiksēts risinājumu un līdzekļu komplekts, kas raksturīgs konkrētai mikroshēmai, tas nedarbosies kaut kā atkāpties no arhitektūras. Jums tiek dots komandu komplekts, ar kuru palīdzību jūs veicat mijiedarbību ar vidi, nolasot datus no digitālās un analogās ieejas un nosūtot signālus pievadiem, izmantojot izejas.

Turklāt jūs varat veikt aprēķinus, saglabāt datus reģistros vai ROM, kā arī darboties ar datiem, kas iesvītroti mikrokontrollera atmiņā. Būtībā tas ir darba ar mikrokontrolleriem mērķis un iezīmes.

Programmējamās loģiskās integrētās shēmas (FPGA) atšķiras ar to, ka, programmējot ierīci, jūs pats izveidojat arhitektūru no pamata loģikas elementiem. Tādējādi jūs iegūstat lielu mikroshēmas ātrumu un elastību. Tas ļauj, nemainot vienu mikroshēmu, veikt vairākus projektus.

Parasti iekšējo FPGA ierīci var iedalīt trīs galvenajās grupās:

1. Loģisko elementu masīvs (makrošūnas, loģiski bloki).

2. Ievades / izvades bloki (IO).

3. Sakaru līnijas starp tām un ierīci, kas kontrolē šos savienojumus.

Tomēr šāda strukturēšana ir ļoti vispārināta, mēs sīkāk apsvērsim šo jautājumu turpmāk.

Programmējot, jūs savienojat elementus tāpat kā jūs, saliekot ierīci no atsevišķiem elementiem un savienojot to ieejas un izejas ar vadītājiem.

Piezīme:

Galvenā atšķirība starp FPGA un mikrokontrolleriem ir tā, ka mikrokontrollerī nevar mainīt iekšējos savienojumus starp vienkāršākajiem elementiem, un programmēšana un darbs ar tiem balstās uz savienojumu reģistrēšanu FPGA.

Mikrokontrolleru izvēle balstās uz daudziem kritērijiem, piemēram:

-

Ātrums un pulksteņa ātrums;

-

ROM un RAM apjoms;

-

Ieeju un izeju skaits.

Citas funkcionālās funkcijas un perifērijas ierīces, piemēram, sakaru līniju un protokolu atbalsts (I2C, viena vada, PWM signāls utt.).

Izvēloties FPGA, galvenais kritērijs ir programmējamo bloku skaits - ar tiem vajadzētu būt pietiekami, lai izpildītu uzdevumu.

Atkarībā no konkrētās FPGA bloku skaits var mainīties plašās robežās un attiecīgi arī izmaksas.

Mikrokontrolieris secīgi veic visas operācijas, kas paredzētas tās programmā, savukārt FPGA bloki uzdevumu veic paralēli un neatkarīgi viens no otra, tāpēc šo ierīču salīdzināšana pēc takts frekvences ir nepraktiska. Viņu darbības princips ir pārāk atšķirīgs.

Sugas

Pašlaik ir svarīgi divi galvenie FPGA veidi:

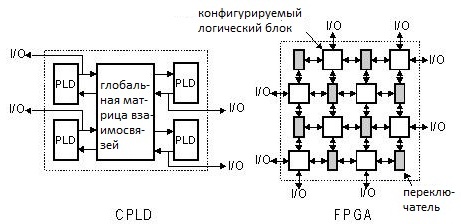

1. CPLD (Complex Programmable Logic Device - Programmable Logic Integrated Circuit, faktiski šī ir FPGA tā klasiskajā izpratnē). Tam parasti ir iebūvēta neizdzēšamā atmiņa, kurā tiek ielādēta programmaparatūra.

Iekšējā struktūra ir veidota uz makrošūnu vai loģisko bloku matricas, un tajās esošo elementu skaits ir simtiem un tūkstošiem gabalu. Savas relatīvās vienkāršības dēļ tie ir lētāki nekā nākamā veida programmējamā loģika. Tas viss noved pie tā, ka CPLD galvenokārt tiek izmantots ķēdēs, kur ir nepieciešams liels ātrums un liels skaits izvadu, vienlaikus veicot vienkāršus uzdevumus.

2. FPGA (lauka programmējams vārtu masīvs - lietotāja programmējams vārtu masīvs, tomēr to bieži sauc par FPGA) - attīstītākas un sarežģītākas ierīces, salīdzinot ar CPLD, ir veidotas uz loģiskiem blokiem ar elastīgu pārslēgšanu un satur lielāku elementu skaitu (desmitiem vai simtiem tūkstošu gabalu).

Programmaparatūra parasti tiek glabāta ārējā neizdzēšamā atmiņā. Papildus vienkāršākajiem loģiskajiem elementiem FPGA var saturēt gatavus blokus jebkādu darbību veikšanai, piemēram, DSP signālu apstrādes blokus. Tas viss ļauj jums ieviest procesoru, signālu apstrādes ierīces un citas sarežģītas ierīces.

Interesanti:

Lai gan faktiski neizdzēšamas atmiņas klātbūtne nepadara programmējamu loģisko CPLD. Tas ir daļēji maldinošs. Galvenā atšķirība starp CPLD un FPGA ir iekšējā struktūra.

Iekšējā CPLD ierīce ir parādīta sīkāk zemāk redzamajā attēlā.

Un tā makrošūnas aptuvenā shēma izskatās šādi:

Makrošūnu veido programmējami multipleksori, sprūdaini (viens vai vairāki) un vairākās versijās veido izejas FB signālu grupu.

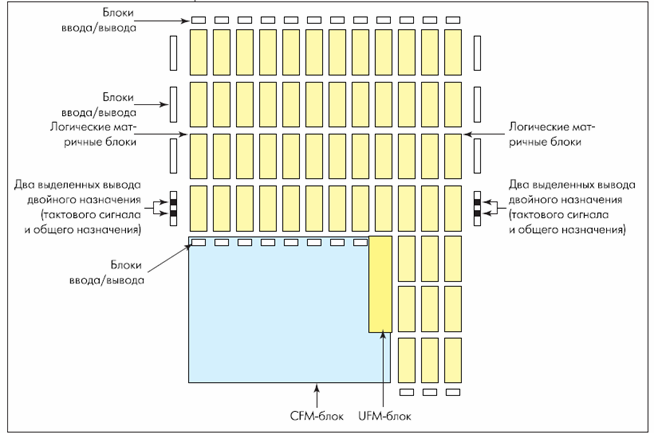

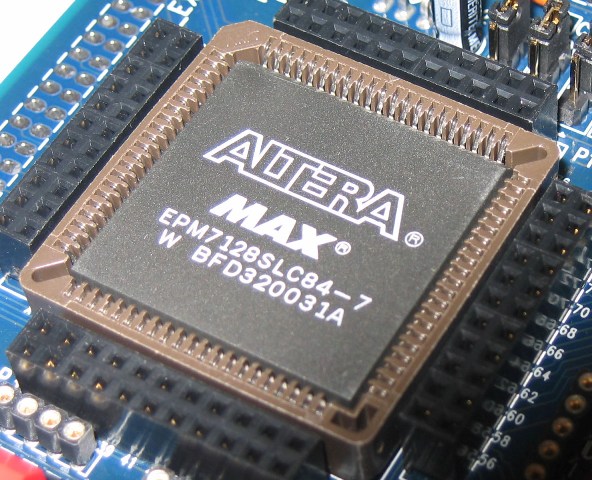

Šis ir vēl viens piemērs - CPLD mikroshēmu saimes MAX II firmas Altera blokshēma.

Un tās pašas ģimenes mikroshēmu strukturālais plāns.

Makrošūnu vidējās riepas tiek piešķirtas, izmantojot mezglu, piemēram, izplatītāju angļu valodā. tas izklausās kā loģikas sadalītājs, kas parādīts zemāk redzamajā diagrammā, tajā parādīta arī komutācijas matrica (globālais maršrutēšanas baseins), un izejā makrošūnām (makrošūnām) ir divas atgriezeniskās saites.

Mikroshēmas ārējās izejas ir savienotas ar makrošūnu izvadiem caur citu bloku (matricu) - ORP (Output Routing Pool), ņemiet vērā, ka caur to INPUT loģika ir savienota ar GRP, kā parādīts attēlā zemāk.

Piezīme:

Dažiem CPLD ir ts tiešās ieejas (Direct Input) - tās ir tieši savienotas ar šūnu ieejām, kas samazina kavēšanos.

FPGA struktūrai ir šāda forma:

-

L - loģiski konfigurējams bloks;

-

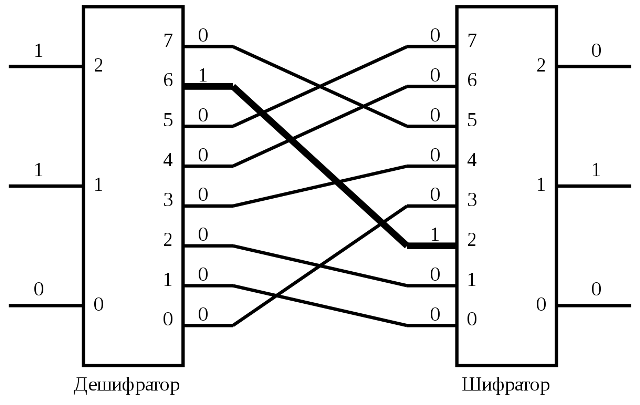

S (aizstāšanas bloks) - aizstāšanas bloks, tas saņem noteiktu bitu skaitu vienā kustībā, pārveido saskaņā ar noteiktu algoritmu un izejā izvada atšķirīgu bitu skaitu. Citiem vārdiem sakot, dekodētājs, šifrētājs un slēdzis.

-

C (savienojuma bloks) - savienojuma bloks.

S-blokshēma:

Programmēšana

HDL (aparatūras apraksta valoda) - šī ir valoda, kurā tiek ieprogrammēti FPGA. Populāri un daudzpusīgi ir Verilog HDL un VHDL. Pastāv arī citas valodas, piemēram, tās, kas raksturīgas ražotājiem, piemēram, AHDL ALTERA izstrādājumiem.

Grafiskā programmēšana ir pieejama izstrādātājiem, kuri strādā ar FPGA. Tas ir, jūs varat vienkārši uzzīmēt loģiskās shēmas vai apvienot kodu ar grafiku. Pēdējo sauc par moduļu attīstības metodi, kad tiek noteikti īpaši moduļi, un augšējais modulis, kurā viss tiek apvienots, tiek ieprogrammēts grafiski.

Populāru ražotāju un sēriju piemēri

Rakstīšanas laikā slavenākie ir divu ražotāju produkti.

-

Altera (dibināta 1983. gadā);

-

Ksilinx (dibināts 1984. gadā).

Altera ir vairākas lielas programmējamas loģikas sērijas:

-

MAX, MAX II, MAX IIZ;

-

7000S;

-

3000A;

-

MAX V;

-

Ciklons

-

Ārija;

-

Stratix

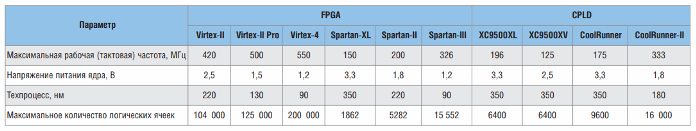

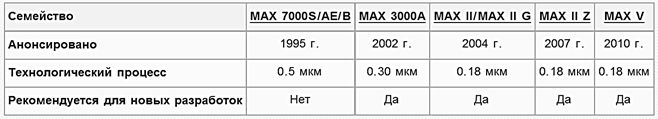

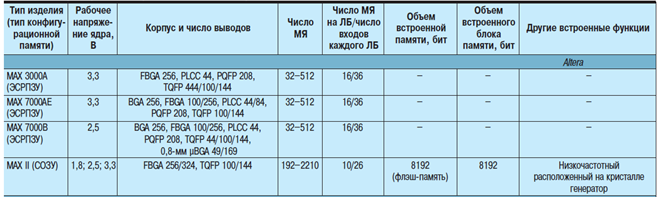

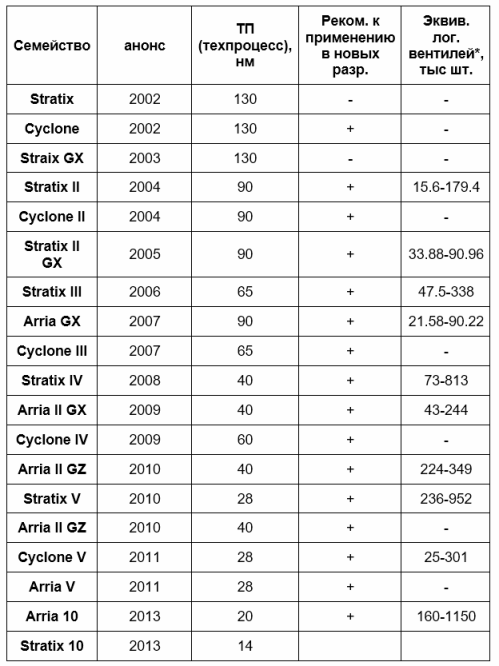

Apsvērsim katru no tiem sīkāk. Zemāk esošajās tabulās ir redzama vispārīga informācija par saimes mikroshēmām.

Altera 3 CPLD CPLD:

-

MAX ir CPLD, kas paredzēts izmantošanai mobilajās ierīcēs, pazīmes ir salīdzinoši zems enerģijas patēriņš un siltuma izkliedēšana. Atkarībā no izlaiduma sarežģītības un gadiem tiek izdalītas šādas modifikācijas:

-

7000S ir novecojis līdz šim, tas tika izlaists 1995. gadā.

-

3000A - izlaists 2002. gadā, tiek ražots, izmantojot 300nm tehnoloģiju. Sastāv no neliela skaita makrošūnu (32–512)

-

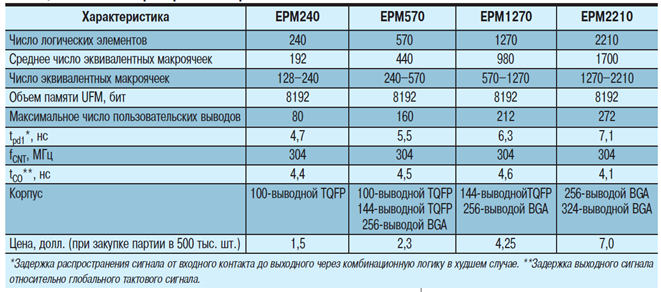

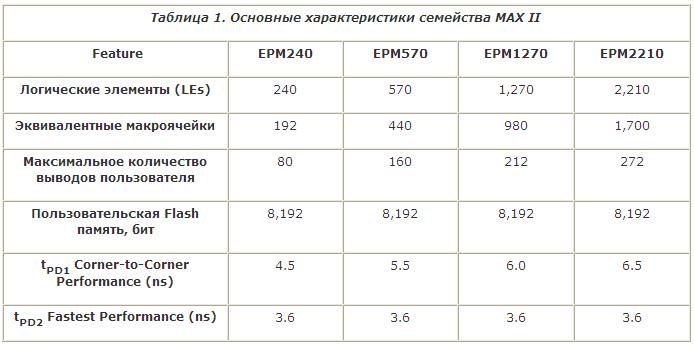

MAX II, kas izlaists 2004. gadā, tiek ražots, izmantojot 100nm tehnoloģiju, sastāv no lielāka skaita vienību (240–2210), kas darbojas frekvencēs līdz 304 MHz. Produkts ir izgatavots gadījumos, kad TQFP 0,5 dzirnavas ir 100 vai vairāk kāju.

-

MAX IIZ - 2007 galvenā iezīme ir samazināts enerģijas patēriņš - tas ir pozitīvs punkts, tomēr frekvences tiek samazinātas līdz 152 MHz. Šīs mikroshēmas tiek barotas no 1,8 V.

-

MAX V - 2010. gads. Tas tiek ražots pēc 180nm tehnoloģijas, tas var saturēt no 40 līdz 2210 blokiem un darboties frekvencēs līdz 152MHz vai ar 304MHz - tas ir atkarīgs no bloku skaita.

FPGA:

-

Ciklons ir budžeta FPGA tipa mikroshēma. Ir piecas paaudzes, kuras apzīmē ar grieķu numuriem (attiecīgi no I līdz V). Pirmā paaudze tika uzsākta 2002. gadā, tika ražota, izmantojot 180nm tehnoloģiju, bet piektā paaudze tika izlaista 2011. gadā un tika ražota, izmantojot 28nm tehnoloģiju. Ir vērts atzīmēt, ka visas paaudzes joprojām ir aktuālas.

-

Ārija - attiecas arī uz vidēja līmeņa FPGA.

-

Stratix - jaudīgi FPGA.

Zemāk ir Altera FPGA programmējamas loģiskās šarnīra tabulas.

Un pilns galds pie saites:https://e.imadeself.com/lv/tablitsa.docx

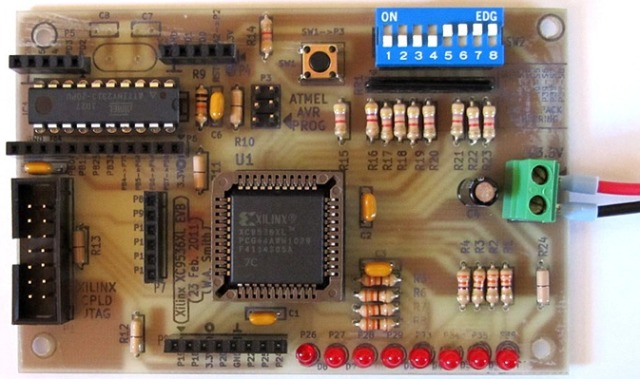

Ražotājs Xilinx CPLD tika parādīts sērijās:

-

XC9500XL no 36-288 makrošūnām. Tie darbojas frekvencēs līdz 178 MHz, un modeļi ar 288 makrošūnām ar 208 MHz. To veic tāpat kā mazos gadījumos ar 44 tapām (vadiem) 0,8 mm attālumā viens no otra - šādus gadījumus uzskata par viegli pielodējamiem. Pieejams arī ar 64 un 100 kājiņām ar soli 0,5 mm, kā arī ar modeļiem PLCC tipa korpusos.

-

CoolRunner-II sērija ir energoefektīva, bet produktīva CPLD. Funkciju baro ar 1,8 V spriegumu, ieejas un izejas ir paredzētas darbībai diapazonā no 1,5 līdz 3,3 V. Tie sastāv no 32-512 makrošūnām un tiek ražoti, izmantojot 180nm tehnoloģiju. Atkarībā no šūnu skaita tās darbojas frekvenču diapazonā no 179 līdz 323 MHz, un jo mazākas ir šūnas, jo lielāku frekvenci viņi šajā gadījumā var strādāt. Tie ir sastopami dažādos gadījumos, ieskaitot viegli pielodētus, tāpat kā iepriekš apskatīto sēriju mikroshēmas.

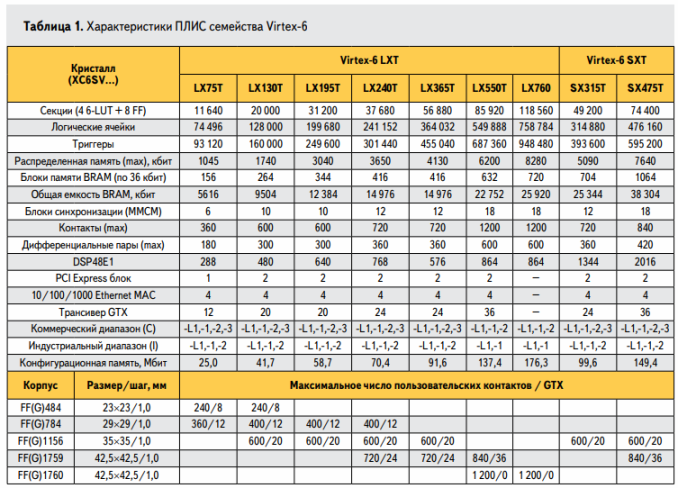

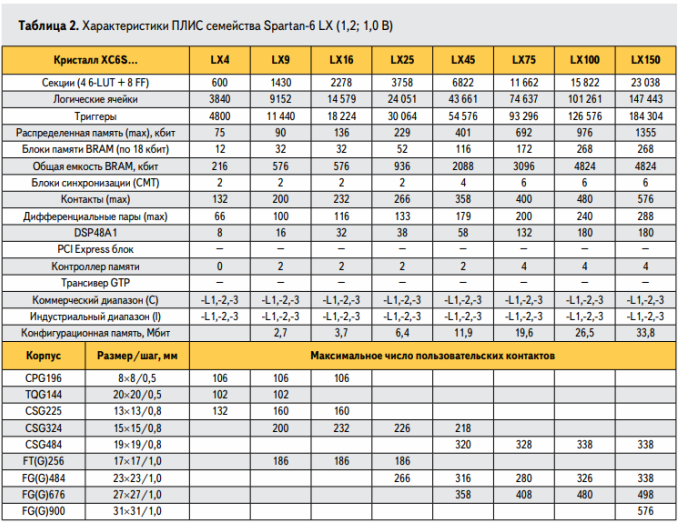

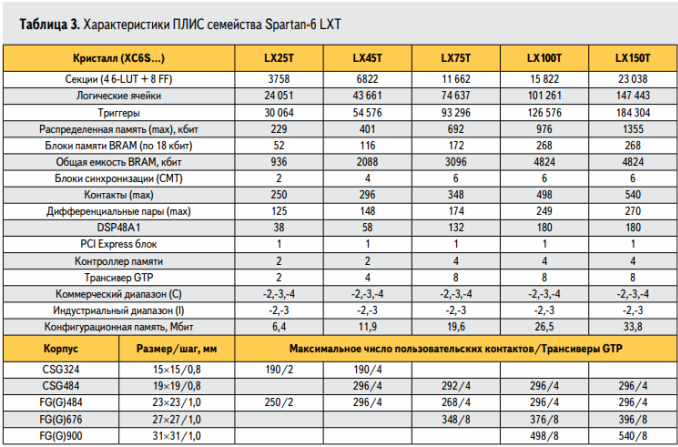

Xilinx uzņēmums netika garām un FPGA:

-

Spartan-6 - sastāv no 6 ievades loģiskajiem blokiem, to skaits ir diapazonā no 3840-147443 gabaliem. Interesanti, ka tie var saturēt kontrolierus datu apmaiņai, piemēram, DDR2, DDR3, PCI-EXPRESS, Ethernet 1Gbit, SerialATA utt.

-

Vitrex-7 sērija ir sarežģīta, mikroshēmas var saturēt līdz 2 000 000 loģikas blokiem un 1200 kontaktiem.

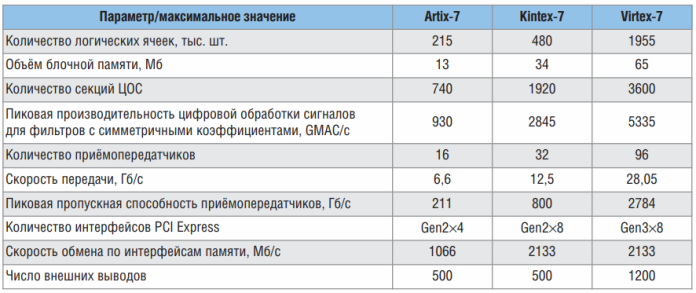

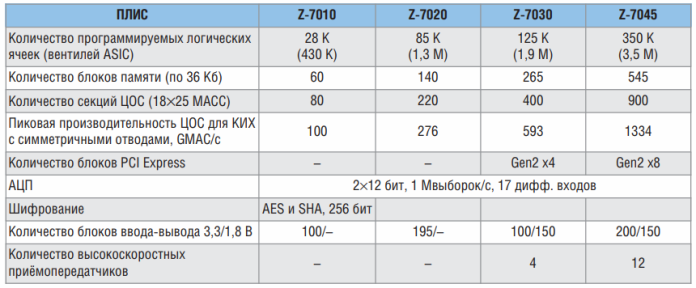

Zemāk jūs atradīsit kopsavilkuma tabulas ar CPLD un FPGA specifikācijām no Xilinx 6 un 7 sērijām, kā arī Zynq-7000.

Secinājums

FPGA un PPVM ražo arī citi uzņēmumi, piemēram, Lattice Semiconductor (2002. gadā sāka ražot FPGA), Actel un tā labi pazīstamie mūsu vietnes lasītāji. mikrokontrolleri ATMEL un daudzi citi. Pēc programmējamas loģikas ir iespējams ieviest vairākas ierīces, vienā ierīcē īstenot paralēlus aprēķinus, kas neatkarīgi viens no otra, tomēr mājas projektiem to pirkšana bieži ir finansiāli nepamatota, bet ražošanas mērogā diezgan saprātīga kā alternatīva pielāgotajām integrētajām shēmām.

P.S.Noskatieties video, tajā redzēsit Nintendo spēļu konsoles ieviešanas piemēru FPGA:

Skatīt arī vietnē e.imadeself.com

: