Kategorie: Obvody mikrokontrolérů

Počet zobrazení: 21445

Komentáře k článku: 0

Co je FPGA jednoduchý jazyk pro začátečníky

S čím je spojená digitální elektronika? Za prvé, s logickými prvky A NEBO NE. Dále se do paměti dostanou posuvné registry, dekodéry, multiplexery atd. S rostoucí složitostí elektronických zařízení a trendem směrem k miniaturizaci se však výroba zařízení založených na integrovaných obvodech (IC) z výše uvedených složek stala obtížnější, vlastní IC požadované topologie a obvodů se ukázaly jako užitečné, pouze pokud bylo zařízení replikováno ve velkém počtu, v jiných případech to bylo nepřiměřeně drahé.

Cesta ven z této situace byl vývoj programovatelných integrovaných logických obvodů (ve zkratce FPGA, cizí zkratka jako programovatelné logické zařízení, PLD). Co je to a kde se používá, řekneme v tomto článku.

Rozdíly od mikrokontrolérů

Se slovem „programovatelné“ se spojuje většina začátečníků s mikrokontroléry. Přestože jsou také programovány, FPGA jsou úplně jiné zařízení.

Pro vývojáře v mikrokontrolérech je k dispozici pevná sada řešení a nástrojů, které jsou vlastní konkrétnímu čipu, nebude se v žádném případě chtít vzdát architektury. Dostáváte sadu příkazů, kterými provádíte operace interakce s prostředím, čtením dat z digitálních a analogových vstupů a odesíláním signálů do akčních členů pomocí výstupů.

Kromě toho můžete provádět výpočty, ukládat data do registrů nebo ROM a také pracovat s daty blikajícími v paměti mikrokontroléru. V zásadě je to účel a vlastnosti práce s mikrokontroléry.

Programovatelné logické integrované obvody (FPGA) se liší tím, že při programování zařízení sami vytváříte architekturu ze základních logických prvků. Tím získáte vysokou rychlost a flexibilitu čipu. Díky tomu je možné bez výměny jednoho čipu vytvořit řadu projektů.

Obecně lze interní zařízení FPGA rozdělit do tří hlavních skupin:

1. Pole logických prvků (makrobuňky, logické bloky).

2. Vstupně / výstupní bloky (IO).

3. Komunikační linky mezi nimi a zařízením, které tato připojení řídí.

Takové strukturování je však velmi zobecněné, tuto otázku budeme podrobněji rozebírat níže.

Programováním spojíte prvky stejným způsobem, jako byste sestavili zařízení z jednotlivých prvků a spojili jejich vstupy a výstupy s vodiči.

Poznámka:

Hlavní rozdíl mezi FPGA a mikrokontroléry spočívá v tom, že v mikrokontroléru nemůžete změnit interní spojení mezi nejjednoduššími prvky a programování a práce s nimi je založena na registraci připojení.

Výběr mikrokontrolérů je založen na mnoha kritériích, jako například:

-

Rychlost a rychlost hodin;

-

Množství ROM a RAM;

-

Počet vstupů a výstupů.

Další funkční vlastnosti a periferie, jako je podpora komunikačních linek a protokolů (I2C, jednovodičový, PWM signál atd.).

Při výběru FPGA je hlavním kritériem počet programovatelných bloků - měly by stačit k provedení úlohy.

V závislosti na konkrétním FPGA se počet bloků může lišit v širokých mezích a podle toho náklady.

Mikrokontrolér provádí postupně všechny operace předepsané ve svém programu, zatímco bloky FPGA vykonávají úkol paralelně a nezávisle na sobě, proto je porovnání těchto zařízení podle hodinové frekvence nepraktické. Jejich princip fungování je příliš odlišný.

Druhy

V současné době jsou relevantní dva hlavní typy FPGA:

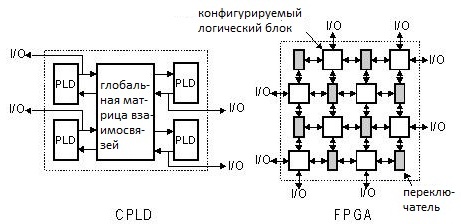

1. CPLD (Složité programovatelné logické zařízení - integrovatelný obvod s programovatelnou logikou, ve skutečnosti se jedná o FPGA v jeho klasickém smyslu). Obvykle má vestavěnou energeticky nezávislou paměť, do které se nahraje firmware.

Vnitřní struktura je postavena na matici makrobuněk nebo logických bloků a počet prvků v nich leží v rozmezí stovek a tisíců kusů. Vzhledem ke své relativní jednoduchosti jsou levnější než další typ programovatelné logiky. To vše vede k tomu, že CPLD se používá hlavně v obvodech, kde je potřeba vysoká rychlost a velký počet výstupů při provádění jednoduchých úkolů.

2. FPGA (Field Programmable Gate Array - User Programmable Gate Array, často se však označuje jako FPGA) - vyspělejší a složitější zařízení ve srovnání s CPLD jsou postavena na logických blocích s flexibilním přepínáním a obsahují větší počet prvků (desítky nebo stovky tisíc kusů).

Firmware je obvykle uložen v externí energeticky nezávislé paměti. Kromě nejjednodušších logických prvků mohou FPGA obsahovat hotové bloky pro provádění jakýchkoli operací, například bloky zpracování DSP signálu. To vše vám umožňuje implementovat procesor, zařízení pro zpracování signálu a další složitá zařízení.

Zajímavé:

I když ve skutečnosti přítomnost energeticky nezávislé paměti neumožňuje programovatelnou logiku CPLD. To je částečně zavádějící. Hlavní rozdíl mezi CPLD a FPGA je vnitřní struktura.

Interní zařízení CPLD je podrobněji znázorněno na obrázku níže.

A přibližné schéma jeho makrobuněk vypadá takto:

Makrobunka se skládá z programovatelných multiplexerů, triggerů (jednoho nebo více) a tvoří skupinu výstupních FB signálů v několika verzích.

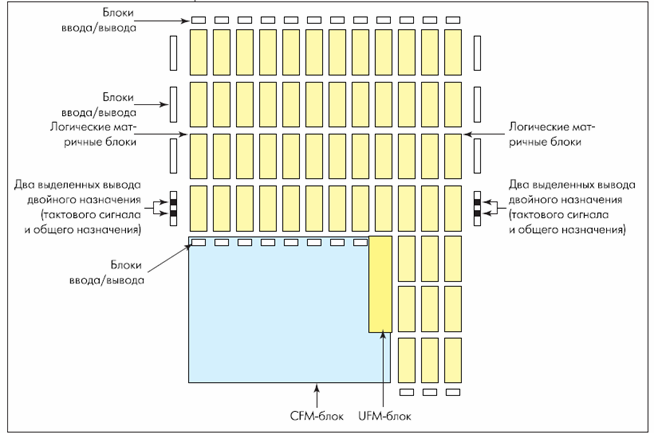

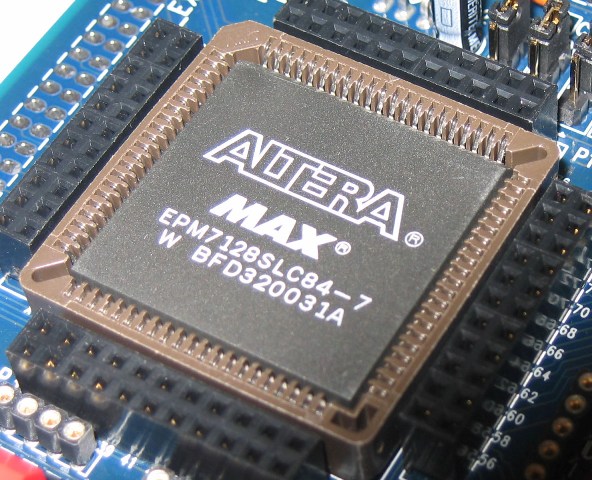

Následuje další příklad - blokové schéma čipu CPLD z rodiny čipů Altera MAX II.

A strukturální plán čipů stejné rodiny.

Střední pneumatiky jsou přiřazeny makrobuněk pomocí uzlu, jako je distributor v angličtině. Zní to jako logický alokátor, který je zobrazen na obrázku níže, také ukazuje matici Global Routing Pool a na výstupních makrobunkách mají dvě zpětné vazby.

Externí výstupy mikroobvodu jsou připojeny k výstupům makrobuněk prostřednictvím dalšího bloku (matice) - ORP (Output Routing Pool), všimněte si, že skrze něj je logika INPUT připojena k GRP, jak ukazuje obrázek níže.

Poznámka:

Některé CPLD mají tzv přímé vstupy (přímý vstup) - jsou přímo připojeny ke vstupům buněk, což snižuje zpoždění.

Struktura FPGA má tvar:

-

L - logický konfigurovatelný blok;

-

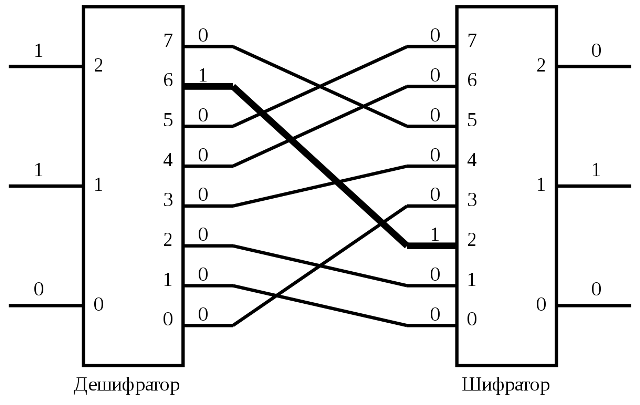

S (substituční blok) - substituční blok, přijímá určitý počet bitů na tah, převádí podle určitého algoritmu a na výstupu vydává jiný počet bitů. Jinými slovy, dekodér, šifrovač a přepínač.

-

C (připojovací blok) - připojovací blok.

S-blokové schéma:

Programování

HDL (Hardware Description Language) - to je jazyk, pomocí kterého jsou programovány FPGA. Populární a univerzální jsou Verilog HDL a VHDL. Existují i jiné jazyky, například jazyky specifické pro výrobce, například AHDL pro produkty ALTERA.

Grafické programování je k dispozici vývojářům, kteří pracují s FPGA. To znamená, že můžete jednoduše nakreslit logické obvody nebo kombinovat kód s grafikou. Ten se nazývá modulární vývojová metoda, když jsou předepsány specifické moduly, a horní modul, ve kterém je vše kombinováno, je programován graficky.

Příklady populárních výrobců a řad

V době psaní jsou nejznámější produkty dvou výrobců.

-

Altera (založená v roce 1983);

-

Xilinx (založena v roce 1984).

Altera má několik hlavních sérií programovatelné logiky:

-

MAX, MAX II, MAX IIZ;

-

7000S;

-

3000A;

-

MAX V;

-

Cyklón

-

Arria;

-

Stratix

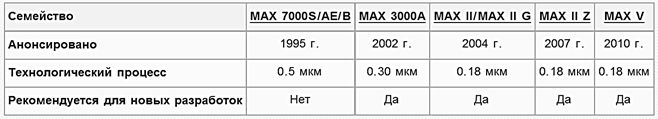

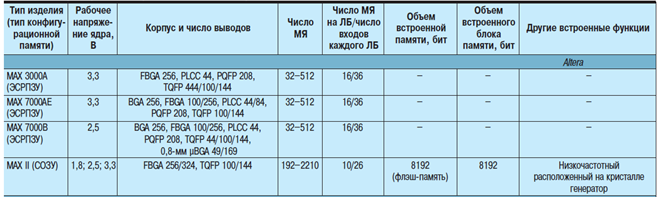

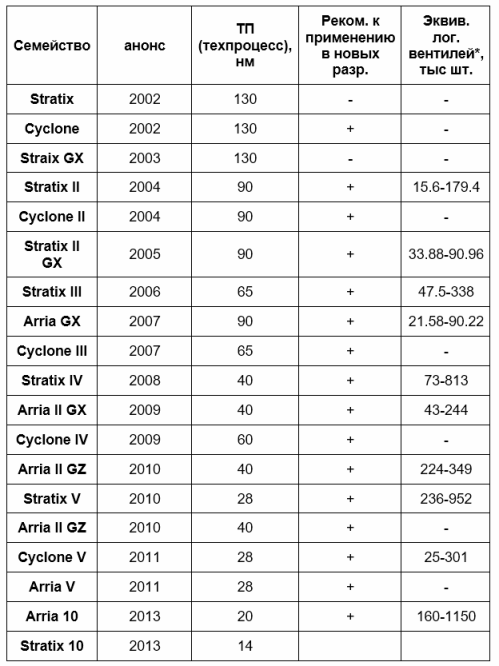

Podívejme se na každou z nich podrobněji. V následujících tabulkách jsou uvedeny obecné informace o čipech rodiny.

Altera 3 CPLD CPLD:

-

MAX je CPLD pro použití v mobilních zařízeních, charakteristickým znakem je relativně nízká spotřeba energie a odvod tepla. V závislosti na složitosti a letech vydání se rozlišují následující modifikace:

-

7000S je zastaralý, byl vydán v roce 1995.

-

3000A - vydané v roce 2002, je vyrobeno pomocí technologie 300nm. Skládá se z malého počtu makrobuněk (32-512)

-

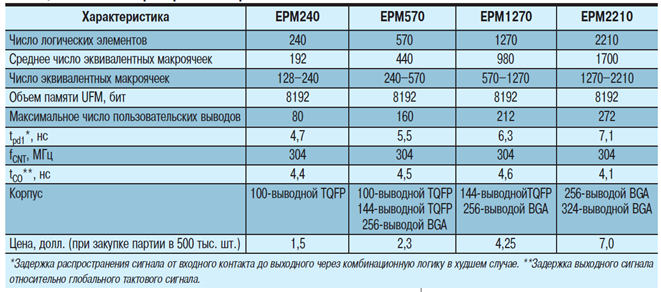

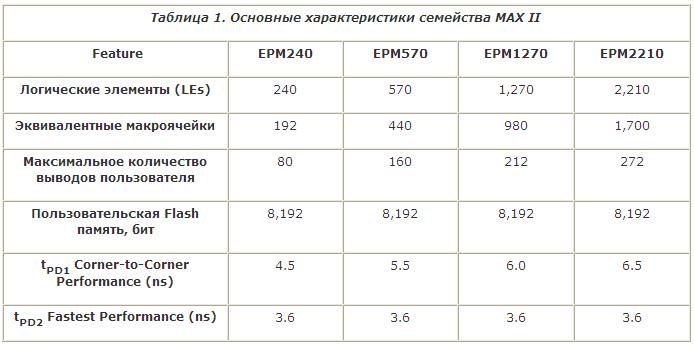

MAX II vydané v roce 2004, je vyrobeno pomocí 100nm technologie, sestává z většího počtu jednotek (240-2210) pracujících na frekvencích až 304 MHz. Výrobek se vyrábí v případech mlýna typu TQFP 0,5 se 100 nebo více nohami.

-

MAX IIZ - 2007, hlavní funkcí je snížená spotřeba energie - to je pozitivní bod, ale frekvence jsou sníženy na 152 MHz. Tyto mikroobvody jsou napájeny z 1,8 V.

-

MAX V - rok 2010. Vyrábí se podle technologie 180nm, může obsahovat 40 až 2210 bloků a pracuje na frekvencích až 152MHz nebo 304MHz - záleží na počtu bloků.

FPGA:

-

Cyclone je rozpočet typu FPGA. Existuje pět generací, které jsou označeny řeckými čísly (od I do V). První generace byla uvedena na trh v roce 2002 a byla vyrobena pomocí technologie 180nm a pátá generace vyšla v roce 2011 a byla vyrobena pomocí technologie 28nm. Stojí za zmínku, že všechny generace zůstávají relevantní.

-

Arria - také se odkazují na FPGA středního rozsahu.

-

Stratix - výkonné FPGA.

Níže jsou programovatelné logické kontingenční tabulky Altera FPGA.

A celý stůl na odkazu:https://e.imadeself.com/cs/tablitsa.docx

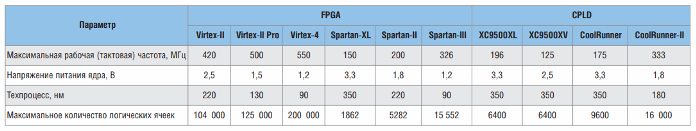

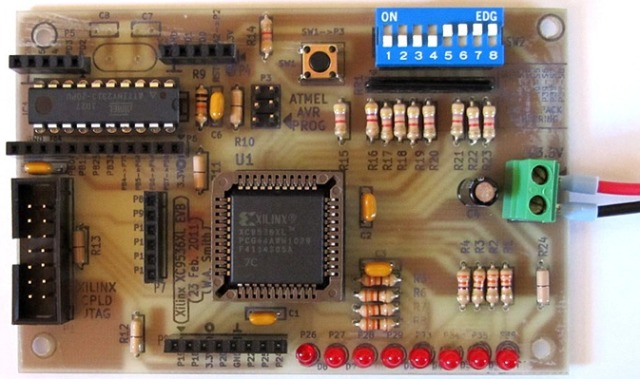

Výrobce Xilinx CPLD představil v sérii:

-

XC9500XL z 36-288 makrobuněk. Fungují na frekvencích až 178 MHz a modely na 288 makrobuněk při 208 MHz. Provádí se jako v malých případech se 44 kolíky (vodítky) ve vzdálenosti 0,8 mm od sebe - tyto případy se považují za snadno pájené. K dispozici také s 64 a 100 nohami v krocích po 0,5 mm, stejně jako modely v krabičkách typu PLCC.

-

Řada CoolRunner-II je energeticky efektivní a přesto produktivní CPLD. Funkce je napájena napětím 1,8 V, vstupy a výstupy jsou navrženy tak, aby fungovaly v rozsahu 1,5 až 3,3 V. Skládají se z 32-512 makrobuněk a jsou vyráběny pomocí technologie 180nm. V závislosti na počtu buněk pracují ve frekvenčním rozsahu 179 až 323 MHz a čím jsou buňky menší, tím více v tomto případě mohou pracovat. Nacházejí se v různých případech, včetně snadno pájených, jako v mikroobvodech výše uvedené řady.

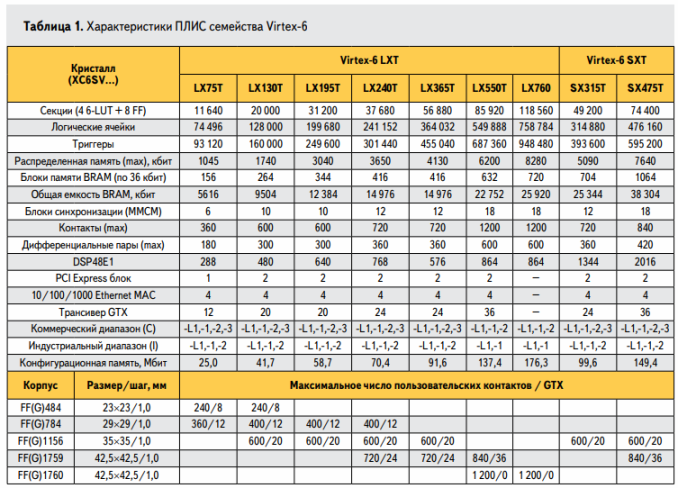

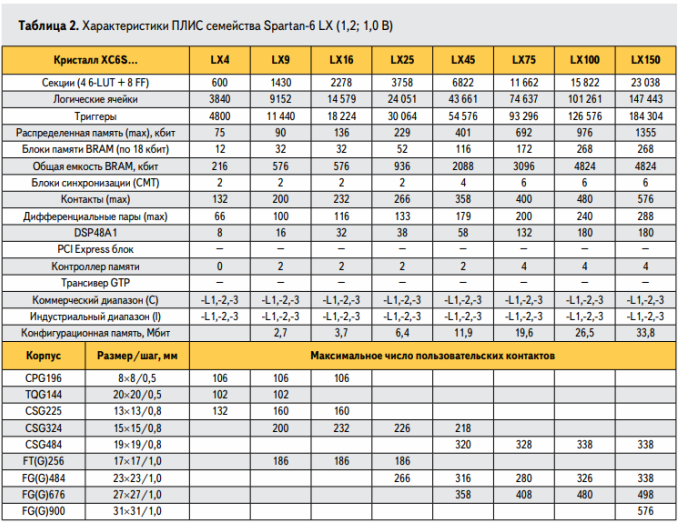

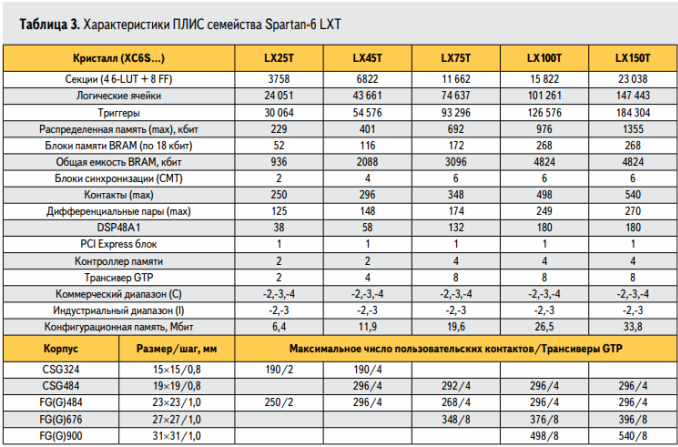

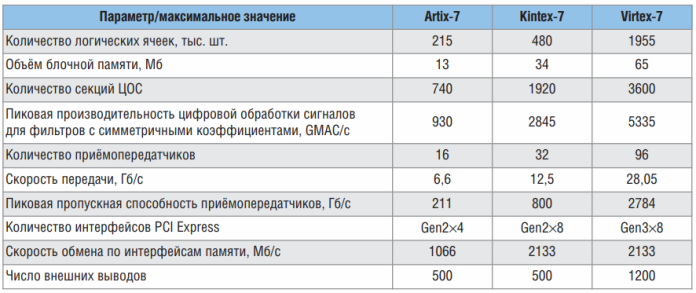

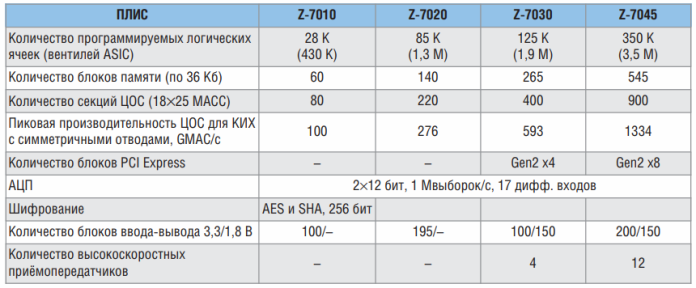

Společnost Xilinx neprošla kolem a FPGA:

-

Spartan-6 - skládá se ze 6-vstupních logických bloků, jejich počet leží v rozmezí 3840-147443 kusů. Zajímavé v tom, že mohou obsahovat řadiče pro výměnu dat, jako jsou DDR2, DDR3, PCI-EXPRESS, Ethernet 1Gbit, SerialATA atd ...

-

Série Vitrex-7 je komplexní, mikroobvody mohou obsahovat až 2 000 000 logických bloků a 1 200 kontaktů.

Níže naleznete souhrnné tabulky se specifikacemi CPLD a FPGA ze série Xilinx 6 a 7 a Zynq-7000.

Závěr

FPGA a PPVM jsou vyráběny také jinými společnostmi, jako je Lattice Semiconductor (v roce 2002 začala vyrábět FPGA), Actel a jeho známé čtenáře našich stránek. mikrokontroléry ATMEL a mnoho dalších. V programovatelné logice je možné implementovat několik zařízení, provádět paralelní výpočty nezávisle na sobě v jednom zařízení, avšak u domácích projektů je jejich nákup často finančně neopodstatněný, ale ve výrobním měřítku docela rozumný, jako alternativa k zakázkovým integrovaným obvodům.

P.S.Podívejte se na video, v něm uvidíte příklad implementace herní konzole Nintendo na FPGA:

Viz také na e.imadeself.com

: